Brought to You by

Like the book? Buy it!

#### WORDWARE GAME MATH LIBRARY

# VECTOR GAME Math Processors

Language Language Language

## Vector Game Math Processors

### **James Leiterman**

Wordware Publishing, Inc.

#### Library of Congress Cataloging-in-Publication Data

Leiterman, James. Vector game math processors / by James Leiterman. p. cm. Includes bibliographical references and index. ISBN 1-55622-921-6 1. Vector processing (Computer science). 2. Computer games--Programming. 3. Supercomputers--Programming. 4. Computer science--Mathematics. 5. Algorithms. I. Title. QA76.5 .L446 2002 004'.35--dc21 2002014988 CIP

© 2003, Wordware Publishing, Inc.

All Rights Reserved

2320 Los Rios Boulevard Plano, Texas 75074

No part of this book may be reproduced in any form or by any means without permission in writing from Wordware Publishing, Inc.

Printed in the United States of America

ISBN 1-55622-921-6

10 9 8 7 6 5 4 3 2 1 0211

Product names mentioned are used for identification purposes only and may be trademarks of their respective companies.

All inquiries for volume purchases of this book should be addressed to Wordware Publishing, Inc., at the above address. Telephone inquiries may be made by calling:

(972) 423-0090

| Preface                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1Introduction1Book Legend7CD Files7Pseudo Vec10Graphics 10111Algebraic Laws11I-VU-Q11Insight13                                                                                                                                                                                                                                             |

| Chapter 2 Coding Standards                                                                                                                                                                                                                                                                                                                         |

| Constants.15Data Alignment15Pancake Memory LIFO Queue.18Stack18Assertions21Memory Systems24RamTest Memory Alignment Test25Memory Header26Allocate Memory (Malloc Wrapper).27Release Memory (Free Wrapper)28Allocate Memory29Allocate (Cleared) Memory29Free Memory — Pointer is Set to NULL29Exercises30                                           |

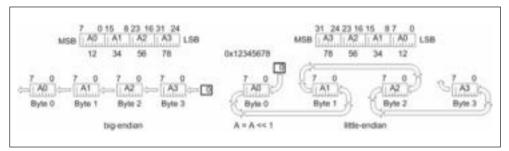

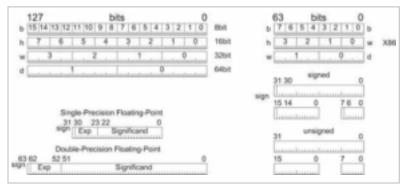

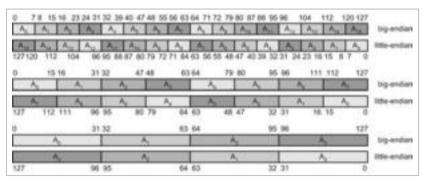

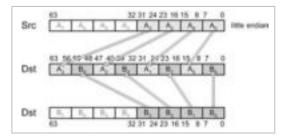

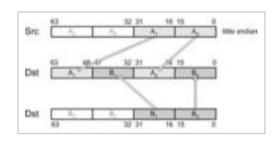

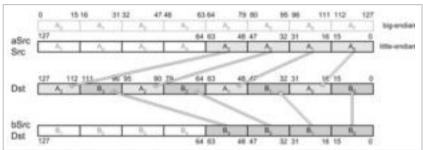

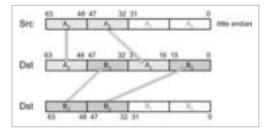

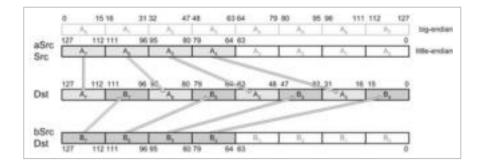

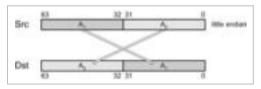

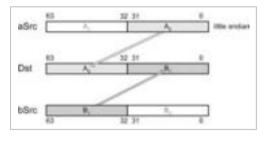

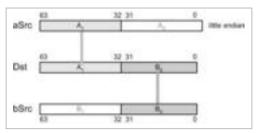

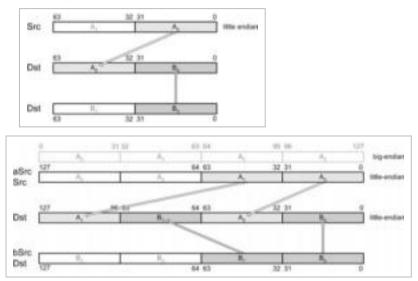

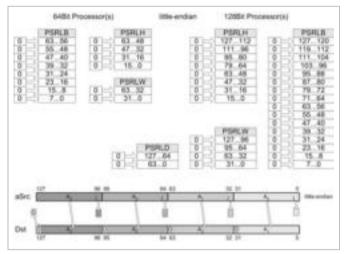

| Chapter 3Processor Differential Insight31Floating-Point 10131Floating-Point Comparison33Processor Data Type Encoding36X86 and IBM Personal Computer38Registers43Destination and Source Orientations43Big and Little Endian44MIPS Multimedia Instructions (MMI)47PS2 VU Coprocessor Instruction Supposition51Gekko Supposition52Function Wrappers54 |

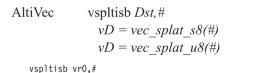

| Single-Precision Function Quad Vector Wrappers62Double-Precision Function Quad Vector Wrappers67Single-Precision Function Vector Wrappers68Double-Precision Function Vector Wrappers71Exercises72Chapter 4Vector Methodologies74Target Processor74Type of Data75AoS75SoA76A Possible Solution?77Packed and Parallel and Pickled81Discrete or Parallel?83Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)01Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Suffle-Packed High Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                 | Integer Function Wrappers                      | 54  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|

| Double-Precision Function Quad Vector Wrappers67Single-Precision Function Vector Wrappers68Double-Precision Function Vector Wrappers71Exercises72Chapter 4Vector Methodologies74Target Processor74Type of Data75AoS75SoA76A Possible Solution?77Packed and Parallel and Pickled81Discrete or Parallel?83Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)116Insert Word into Integer Register (1x16) to (1x16)116Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                    | Single-Precision Function Quad Vector Wrappers | 62  |

| Double-Precision Function Vector Wrappers       71         Exercises       72         Chapter 4       Vector Methodologies       74         Target Processor       74         Type of Data       75         AoS       75         SoA       76         A Possible Solution?       77         Packed and Parallel and Pickled       81         Discrete or Parallel?       83         Algorithmic Breakdown       86         Array Summation       86         Thinking Out of the Box (Hexagon)       90         Vertical Interpolation with Rounding       91         Exercises       94         Chapter 5       Vector Data Conversion       95         Pseudo Vec (X86)       95         Pseudo Vec (MIPS-MMI)       99         Pseudo Vec (MIPS-VU0)       101         Data Interlacing, Exchanging, Unpacking, and Merging       101         Swizzle, Shuffle, and Splat.       114         Vector Splat Immediate Signed Half-Word (8x16-bit)       114         Vector Splat Immediate Signed Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       115         Vector Splat Half-Word (8x16-bit)       116         Insert Word into | Double-Precision Function Quad Vector Wrappers | 67  |

| Exercises       72         Chapter 4       Vector Methodologies       74         Target Processor       74         Type of Data       75         AoS       75         AoS       75         SoA       76         A Possible Solution?       77         Packed and Parallel and Pickled       81         Discrete or Parallel?       83         Algorithmic Breakdown       86         Array Summation       86         Thinking Out of the Box (Hexagon)       90         Vertical Interpolation with Rounding       91         Exercises       94         Chapter 5       Vector Data Conversion       95         (Un)aligned Memory Access       95         Pseudo Vec (X86)       95         Pseudo Vec (MIPS-MMI)       99         Pseudo Vec (MIPS-VU0)       101         Data Interlacing, Exchanging, Unpacking, and Merging       101         Swizzle, Shuffle, and Splat       114         Vector Splat Immediate Signed Byte (16x8-bit)       114         Vector Splat Immediate Signed Half-Word (8x16-bit)       115         Vector Splat Half-Word (8x16-bit)       115         Vector Splat Half-Word (8x16-bit)       116                            | Single-Precision Function Vector Wrappers      | 68  |

| Chapter 4       Vector Methodologies       74         Target Processor       74         Type of Data       75         AoS       75         AoS       76         A Possible Solution?       76         A Possible Solution?       77         Packed and Parallel and Pickled       81         Discrete or Parallel?       83         Algorithmic Breakdown       86         Array Summation       86         Thinking Out of the Box (Hexagon)       90         Vertical Interpolation with Rounding       91         Exercises       94         Chapter 5       Vector Data Conversion       95         (Un)aligned Memory Access       95         Pseudo Vec (X86)       95         Pseudo Vec (MIPS-MMI)       99         Pseudo Vec (MIPS-VU0)       101         Data Interlacing, Exchanging, Unpacking, and Merging       101         Swizzle, Shuffle, and Splat       114         Vector Splat Immediate Signed Byte (16x8-bit)       114         Vector Splat Half-Word (8x16-bit)       115         Vector Splat Half-Word (8x16-bit)       115         Vector Splat Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)            | Double-Precision Function Vector Wrappers      | 71  |

| Target Processor       74         Type of Data       75         AoS       75         SoA       76         A Possible Solution?       77         Packed and Parallel and Pickled       81         Discrete or Parallel?       83         Algorithmic Breakdown       86         Array Summation       86         Array Summation       86         Thinking Out of the Box (Hexagon)       90         Vertical Interpolation with Rounding       91         Exercises       94         Chapter 5       Vector Data Conversion       95         Pseudo Vec (X86)       95         Pseudo Vec (AltiVec)       98         Pseudo Vec (MIPS-MMI)       99         Pseudo Vec (MIPS-VU0)       101         Data Interlacing, Exchanging, Unpacking, and Merging       101         Swizzle, Shuffle, and Splat       114         Vector Splat Immediate Signed Byte (16x8-bit)       114         Vector Splat Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       116         Insert Word from Integer Register (4x16-bit) to (1x16) | Exercises                                      | 72  |

| Target Processor       74         Type of Data       75         AoS       75         SoA       76         A Possible Solution?       77         Packed and Parallel and Pickled       81         Discrete or Parallel?       83         Algorithmic Breakdown       86         Array Summation       86         Array Summation       86         Thinking Out of the Box (Hexagon)       90         Vertical Interpolation with Rounding       91         Exercises       94         Chapter 5       Vector Data Conversion       95         Pseudo Vec (X86)       95         Pseudo Vec (AltiVec)       98         Pseudo Vec (MIPS-MMI)       99         Pseudo Vec (MIPS-VU0)       101         Data Interlacing, Exchanging, Unpacking, and Merging       101         Swizzle, Shuffle, and Splat       114         Vector Splat Immediate Signed Byte (16x8-bit)       114         Vector Splat Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       116         Insert Word from Integer Register (4x16-bit) to (1x16) | Chapter 4 Vector Methodologies                 | 74  |

| Type of Data       75         AoS       75         SoA       76         A Possible Solution?       77         Packed and Parallel and Pickled       81         Discrete or Parallel?       83         Algorithmic Breakdown       86         Array Summation       86         Array Summation       86         Thinking Out of the Box (Hexagon)       90         Vertical Interpolation with Rounding       91         Exercises       94         Chapter 5       Vector Data Conversion       95         (Un)aligned Memory Access       95         Pseudo Vec (X86)       95         Pseudo Vec (RowerPC)       98         Pseudo Vec (MIPS-MMI)       99         Pseudo Vec (MIPS-WU0)       101         Data Interlacing, Exchanging, Unpacking, and Merging       101         Swizzle, Shuffle, and Splat       114         Vector Splat Immediate Signed Byte (16x8-bit)       114         Vector Splat Byte (16x8-bit)       115         Vector Splat Half-Word (8x16-bit)       115         Vector Splat Half-Word (8x16-bit)       115         Vector Splat Half-Word (8x16-bit)       115         Parallel Copy Half-Word (8x16-bit)       115          | •                                              |     |

| AoS75SoA76A Possible Solution?77Packed and Parallel and Pickled81Discrete or Parallel?83Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (AltiVec)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat114Vector Splat Byte (16x8-bit)114Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                    | Type of Data                                   | 75  |

| SoA76A Possible Solution?77Packed and Parallel and Pickled81Discrete or Parallel?83Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (AltiVec)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)116Insert Word into Integer Register (4x16-bit) to (1x16)117Shuffle-Packed Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |     |

| A Possible Solution?77Packed and Parallel and Pickled81Discrete or Parallel?83Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (AltiVec)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)116Insert Word from Integer Register (4x16-bit) to (1x16)117Shuffle-Packed Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |     |

| Packed and Parallel and Pickled81Discrete or Parallel?83Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (PowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                       |                                                |     |

| Discrete or Parallel?83Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (PowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                        |                                                |     |

| Algorithmic Breakdown86Array Summation86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94 <b>Chapter 5Vector Data Conversion95</b> 95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (RowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (1x16) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                   |                                                |     |

| Array Summation.86Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises.94 <b>Chapter 5Vector Data Conversion(</b> Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (RowerPC).98Pseudo Vec (AltiVec).99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)116Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |     |

| Thinking Out of the Box (Hexagon)90Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (RowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |     |

| Vertical Interpolation with Rounding91Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (RowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Thinking Out of the Box (Hexagon)              | 90  |

| Exercises94Chapter 5Vector Data Conversion95(Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (PowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Byte (16x8-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (1x16) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Vertical Interpolation with Rounding           | 91  |

| (Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (PowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |     |

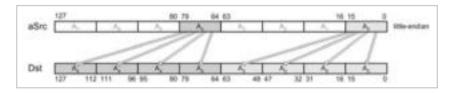

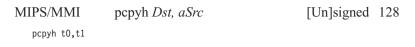

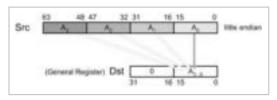

| (Un)aligned Memory Access95Pseudo Vec (X86)95Pseudo Vec (PowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Chapter 5 Vector Data Conversion               | 95  |

| Pseudo Vec (X86)95Pseudo Vec (PowerPC)98Pseudo Vec (AltiVec)99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Immediate Signed Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |     |

| Pseudo Vec (PowerPC).98Pseudo Vec (AltiVec).99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0).101Data Interlacing, Exchanging, Unpacking, and Merging.101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit).114Vector Splat Immediate Signed Half-Word (8x16-bit).115Vector Splat Immediate Signed Half-Word (8x16-bit).115Parallel Copy Half-Word (8x16-bit).115Extract Word into Integer Register (4x16-bit) to (1x16).116Insert Word from Integer Register (1x16) to (4x16-bit).117Shuffle-Packed Low Words (4x16-bit).117Shuffle-Packed High Words (4x16-bit).117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |     |

| Pseudo Vec (AltiVec).99Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Immediate Signed Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |     |

| Pseudo Vec (MIPS-MMI)99Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |     |

| Pseudo Vec (MIPS-VU0)101Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Immediate Signed Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |     |

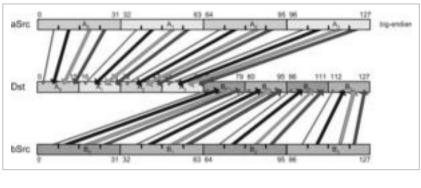

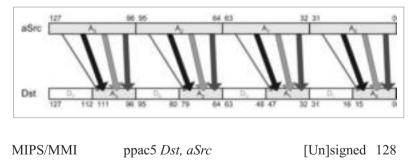

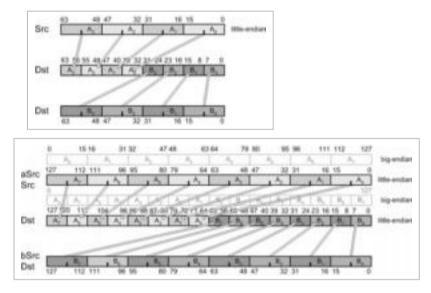

| Data Interlacing, Exchanging, Unpacking, and Merging101Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |     |

| Swizzle, Shuffle, and Splat.114Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |     |

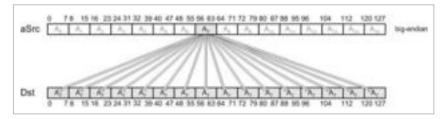

| Vector Splat Immediate Signed Byte (16x8-bit)114Vector Splat Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |     |

| Vector Splat Byte (16x8-bit)114Vector Splat Immediate Signed Half-Word (8x16-bit)115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)117Shuffle-Packed Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |     |

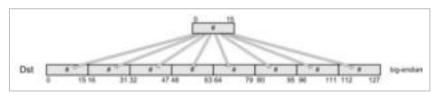

| Vector Splat Immediate Signed Half-Word (8x16-bit).115Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)116Shuffle-Packed Words (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                |     |

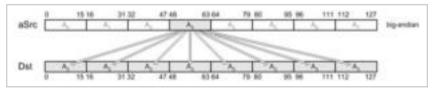

| Vector Splat Half-Word (8x16-bit)115Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)116Shuffle-Packed Words (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                |     |

| Parallel Copy Half-Word (8x16-bit)115Extract Word into Integer Register (4x16-bit) to (1x16)116Insert Word from Integer Register (1x16) to (4x16-bit)116Shuffle-Packed Words (4x16-bit)117Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |     |

| Extract Word into Integer Register (4x16-bit) to (1x16).116Insert Word from Integer Register (1x16) to (4x16-bit).116Shuffle-Packed Words (4x16-bit).117Shuffle-Packed Low Words (4x16-bit).117Shuffle-Packed High Words (4x16-bit).117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |     |

| Insert Word from Integer Register (1x16) to (4x16-bit) 116<br>Shuffle-Packed Words (4x16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |     |

| Shuffle-Packed Words (4x16-bit).117Shuffle-Packed Low Words (4x16-bit).117Shuffle-Packed High Words (4x16-bit).117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |     |

| Shuffle-Packed Low Words (4x16-bit)117Shuffle-Packed High Words (4x16-bit)117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |     |

| Shuffle-Packed High Words (4x16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Shuffle-Packed Low Words (4x16-bit)            | 117 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |     |

| Vector Splat Word (8x16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                |     |

| Shuffle-Packed Double Words (4x32-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                |     |

| Graphics Processor Unit (GPU) Swizzle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | · /                                            |     |

| Data Bit Expansion — RGB 5:5:5 to RGB32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |     |

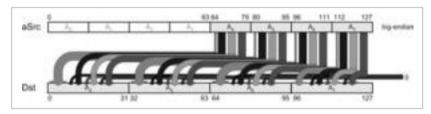

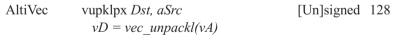

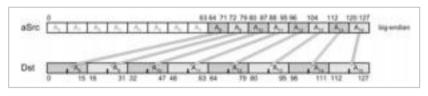

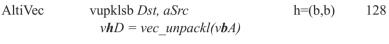

| Vector Unpack Low Pixel16 (4x16-bit) to $(4x32)$ 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |     |

| Vector Unpack High Pixel16 ( $4x16$ -bit) to ( $4x32$ )120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Vector Unpack Low Fixerro (4x10-bit) to (4x32) |     |

| Parallel Extend from 5 Bits                                                                                                                                                   | 121                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Data Bit Expansion.                                                                                                                                                           | 121                                    |

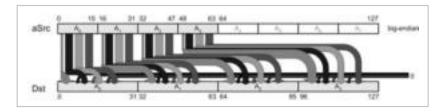

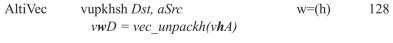

| Vector Unpack Low-Signed Byte (8x8) to (8x16-bit)                                                                                                                             |                                        |

| Vector Unpack High-Signed Byte (8x8) to (8x16-bit)                                                                                                                            |                                        |

| Vector Unpack Low-Signed Half-Word (4x16)                                                                                                                                     |                                        |

| to (4x32-bit)                                                                                                                                                                 | 123                                    |

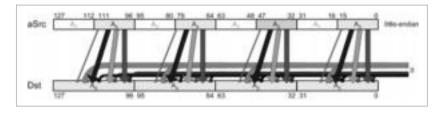

| Vector Unpack High-Signed Half-Word (4x16)                                                                                                                                    |                                        |

| to (4x32-bit).                                                                                                                                                                | 123                                    |

| Data Bit Reduction — RGB32 to RGB 5:5:5                                                                                                                                       | 123                                    |

| Vector Pack 32-bit Pixel to 5:5:5                                                                                                                                             |                                        |

| Parallel Pack to 5 Bits.                                                                                                                                                      |                                        |

| Data Bit Reduction (with Saturation)                                                                                                                                          |                                        |

| Vector Pack Signed Half-Word Signed Saturate                                                                                                                                  |                                        |

| Vector Pack Signed Half-Word Unsigned Saturate                                                                                                                                |                                        |

| Vector Pack Unsigned Half-Word Unsigned Saturate                                                                                                                              |                                        |

| Vector Pack Unsigned Half-Word Unsigned Modulo                                                                                                                                |                                        |

| Vector Pack Signed Word Signed Saturate                                                                                                                                       |                                        |

| Vector Pack Signed Word Unsigned Saturate                                                                                                                                     |                                        |

| Vector Pack Unsigned Word Unsigned Saturate                                                                                                                                   |                                        |

| Exercises                                                                                                                                                                     |                                        |

|                                                                                                                                                                               | 120                                    |

| Chapter 6 Bit Mangling                                                                                                                                                        |                                        |

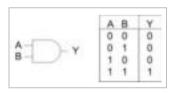

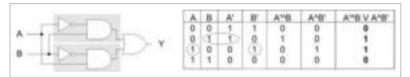

| Boolean Logical AND                                                                                                                                                           | 130                                    |

| Pseudo Vec                                                                                                                                                                    | 131                                    |

| Pseudo Vec (X86)                                                                                                                                                              | 132                                    |

| Pseudo Vec (PowerPC)                                                                                                                                                          | 134                                    |

| Pseudo Vec (MIPS)                                                                                                                                                             | 136                                    |

| Boolean Logical OR                                                                                                                                                            | 138                                    |

| Pseudo Vec                                                                                                                                                                    | 139                                    |

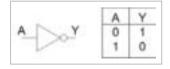

| Boolean Logical XOR (Exclusive OR)                                                                                                                                            | 139                                    |

| Pseudo Vec                                                                                                                                                                    | 140                                    |

| Toolbox Snippet — The Butterfly Switch                                                                                                                                        | 142                                    |

| I-VU-Q                                                                                                                                                                        | 144                                    |

| Boolean Logical ANDC                                                                                                                                                          | 147                                    |

| Pseudo Vec                                                                                                                                                                    | 148                                    |

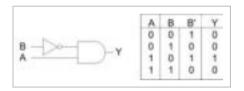

| Boolean Logical NOR (NOT OR)                                                                                                                                                  | 149                                    |

| Pseudo Vec                                                                                                                                                                    |                                        |

| Pseudo Vec (X86)                                                                                                                                                              |                                        |

|                                                                                                                                                                               |                                        |

| Pseudo vec (PowerPC)                                                                                                                                                          | 151                                    |

| Pseudo Vec (PowerPC)                                                                                                                                                          | 151<br>151                             |

| Graphics 101 — Blit                                                                                                                                                           | 151                                    |

| Graphics 101 — Blit                                                                                                                                                           | 151<br>152                             |

| Graphics 101 — Blit                                                                                                                                                           | 151<br>152<br>152                      |

| Graphics 101 — Blit       Blit         Copy Blit       Transparent Blit         Graphics 101 — Blit (MMX)       Sector                                                        | 151<br>152<br>152<br>153               |

| Graphics 101 — Blit       Blit         Copy Blit       Transparent Blit         Transparent Blit       Graphics 101 — Blit (MMX)         Graphics Engine       Sprite Layered | 151<br>152<br>152<br>153<br>153        |

| Graphics 101 — Blit       Blit         Copy Blit       Transparent Blit         Graphics 101 — Blit (MMX)       Sector                                                        | 151<br>152<br>152<br>153<br>153<br>154 |

| Chapter 7 Bit Wrangling                               | 157   |

|-------------------------------------------------------|-------|

| Parallel Shift (Logical) Left                         | . 158 |

| Pseudo Vec                                            | . 159 |

| Pseudo Vec (X86)                                      | . 162 |

| Pseudo Vec (PowerPC)                                  | . 163 |

| Pseudo Vec (MMI)                                      | . 165 |

| Parallel Shift (Logical) Right                        | . 168 |

| Pseudo Vec                                            | . 169 |

| Parallel Shift (Arithmetic) Right.                    | . 170 |

| Pseudo Vec                                            |       |

| Pseudo Vec (X86)                                      | . 175 |

| Pseudo Vec (PowerPC)                                  | . 176 |

| Pseudo Vec (MIPS)                                     |       |

| Rotate Left (or N-Right)                              | . 179 |

| Pseudo Vec                                            | . 180 |

| Pseudo Vec (X86)                                      | . 181 |

| Pseudo Vec (PowerPC)                                  |       |

| Pseudo Vec (MIPS)                                     |       |

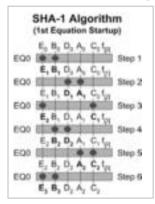

| Secure Hash Algorithm (SHA-1)                         |       |

| Exercises                                             | . 191 |

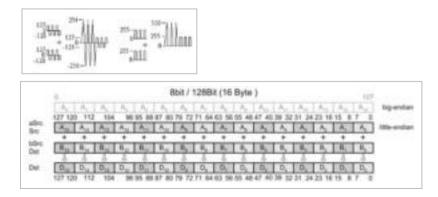

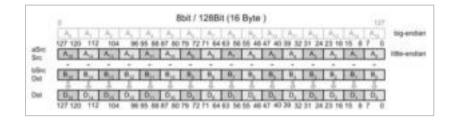

| Chapter 8 Vector Addition and Subtraction             | 192   |

| Vector Floating-Point Addition                        |       |

| Vector Floating-Point Addition with Scalar            |       |

| Vector Floating-Point Subtraction                     |       |

| vmp_VecNeg                                            |       |

| Vector Floating-Point Subtraction with Scalar         |       |

| Pseudo Vec                                            |       |

| Vector Floating-Point Reverse Subtraction             |       |

| Vector Addition and Subtraction (Single-Precision)    |       |

| Pseudo Vec                                            |       |

| Pseudo Vec (X86)                                      | . 201 |

| Pseudo Vec (PowerPC)                                  | . 204 |

| Pseudo Vec (MIPS)                                     | . 205 |

| Vector Scalar Addition and Subtraction                | . 206 |

| Single-Precision Quad Vector Float Scalar Addition    |       |

| Single-Precision Quad Vector Float Scalar Subtraction | . 207 |

| Vector Integer Addition                               | . 208 |

| Pseudo Vec                                            |       |

| Vector Integer Addition with Saturation.              | . 210 |

| Vector Integer Subtraction                            | . 213 |

| Vector Integer Subtraction with Saturation            |       |

| Vector Addition and Subtraction (Fixed Point)         |       |

| Pseudo Vec                                            | . 215 |

| Pseudo Vec (X86)                                      |       |

| Pseudo Vec (PowerPC)                                  | . 218 |

| Pseudo Vec (MIPS)                             | 218   |

|-----------------------------------------------|-------|

| Exercises                                     |       |

| Project                                       |       |

|                                               |       |

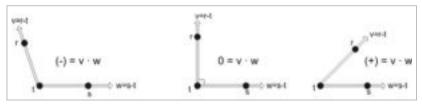

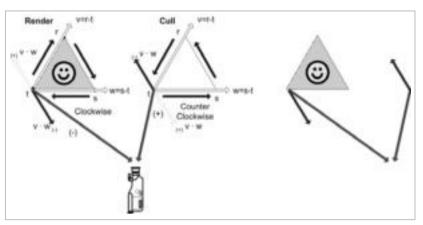

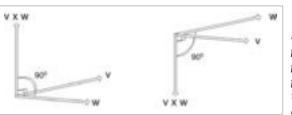

| Chapter 9 Vector Multiplication and Division. | . 221 |

| Floating-Point Multiplication                 |       |

| NxSP-FP Multiplication                        |       |

| (Semi-Vector) DP-FP Multiplication            | 222   |

| SP-FP Scalar Multiplication                   |       |

| DP-FP Scalar Multiplication                   |       |

| NxSP-FP Multiplication — Add                  |       |

| SP-FP Multiplication — Subtract with Rounding | 224   |

| Vector (Float) Multiplication — Add           | 224   |

| Pseudo Vec                                    | 224   |

| Pseudo Vec (X86)                              | 225   |

| Pseudo Vec (PowerPC)                          | 228   |

| Pseudo Vec (MIPS)                             | 229   |

| Vector Scalar Multiplication                  | 230   |

| Pseudo Vec                                    |       |

| Pseudo Vec (X86)                              | 231   |

| Pseudo Vec (PowerPC)                          |       |

| Pseudo Vec (MIPS)                             |       |

| Graphics 101                                  |       |

| Pseudo Vec                                    |       |

| Pseudo Vec (X86)                              |       |

| Pseudo Vec (PowerPC)                          |       |

| Pseudo Vec (MIPS)                             |       |

| Graphics 101                                  |       |

| Vector Floating-Point Division                |       |

| (Vector) SP-FP Division                       |       |

| (Semi-Vector) DP-FP Division                  |       |

| SP-FP Scalar Division                         |       |

| DP-FP Scalar Division                         |       |

| SP-FP Reciprocal (14 bit).                    |       |

| SP-FP Reciprocal (2 Stage) (24 Bit)           |       |

| Pseudo Vec (PowerPC)                          |       |

| Pseudo Vec (MIPS)                             |       |

| Pseudo Vec                                    |       |

| Pseudo Vec (X86)                              |       |

| Pseudo Vec (PowerPC)                          |       |

| Pseudo Vec (MIPS)                             |       |

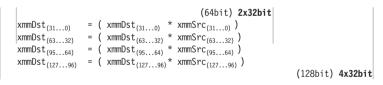

| Packed {8/16/32} Bit Integer Multiplication   |       |

| 8x8-bit Multiply Even                         |       |

| 8x8-bit Multiply Odd                          |       |

| 4x16-bit Multiply Even                        |       |

| 4x16-bit Multiply Odd                         |       |

| TATO-OIL MUMPLY OUV                           | 434   |

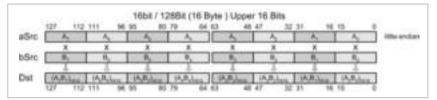

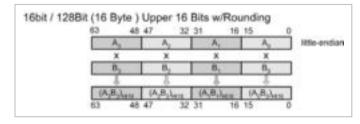

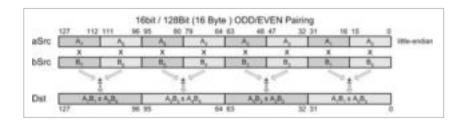

| 8x16-bit Parallel Multiply Half-WordNx16-Bit Parallel Multiplication (Lower)Nx16-bit Parallel Multiplication (Upper)Signed 4x16-bit Multiplication with Rounding (Upper)Unsigned Nx32-bit Multiply EvenInteger Multiplication and Addition/ SubtractionSigned Nx16-bit Parallel Multiplication and AdditionSigned Nx16-bit Parallel Multiplication and SubtractionSigned Nx16-bit Parallel Multiplication and SubtractionSigned 8x16-bit Multiply then Add with Saturation | 253<br>254<br>255<br>255<br>256<br>257<br>257<br>258 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Signed 8x16-bit Multiply Round then Add with<br>Saturation                                                                                                                                                                                                                                                                                                                                                                                                                 | 259                                                  |

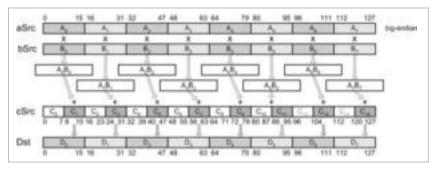

| 16x8-bit Multiply then Quad 32-bit Sum                                                                                                                                                                                                                                                                                                                                                                                                                                     | 260                                                  |

| 8x16-bit Multiply then Quad 32-bit Sum with Saturation                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                      |

| Vector (Integer) Multiplication and Add                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |

| Pseudo Vec                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

| Pseudo Vec (X86)                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |

| Pseudo Vec (MIPS)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |