Ian Parberry

Whitmore Laboratory

Pennsylvania State University, USA

# **Parallel Complexity Theory**

Pitman, London

John Wiley & Sons, Inc., New York, Toronto

## **License Agreement**

This work is copyright <u>Ian Parberry</u>. All rights reserved. The author offers this work, retail value US\$20, free of charge under the following conditions:

- No part of this work may be made available on a public forum (including, but not limited to a web page, ftp site, bulletin board, or internet news group) without the written permission of the author.

- No part of this work may be rented, leased, or offered for sale commercially in any form or by any means, either print, electronic, or otherwise, without written permission of the author.

- If you wish to provide access to this work in either print or electronic form, you may do so by providing a link to, and/or listing the URL for the online version of this license agreement: <a href="http://hercule.csci.unt.edu/ian/books/free/license.html">http://hercule.csci.unt.edu/ian/books/free/license.html</a>. You may not link directly to the PDF file.

- All printed versions of any or all parts of this work must include this license agreement. Receipt of a printed copy of this work implies acceptance of the terms of this license agreement. If you have received a printed copy of this work and do not accept the terms of this license agreement, please destroy your copy by having it recycled in the most appropriate manner available to you.

- You may download a single copy of this work. You may make as many copies as you wish for your own personal use. You may not give a copy to any other person unless that person has read, understood, and agreed to the terms of this license agreement.

- You undertake to donate a reasonable amount of your time or money to the charity of your choice as soon as your personal circumstances allow you to do so. The author requests that you make a cash donation to <a href="The National Multiple Sclerosis Society">The National Multiple Sclerosis Society</a> in the following amount for each work that you receive:

- o \$5 if you are a student,

- o \$10 if you are a faculty member of a college, university, or school,

- o \$20 if you are employed full-time in the computer industry.

Faculty, if you wish to use this work in your classroom, you are requested to:

- o encourage your students to make individual donations, or

- o make a lump-sum donation on behalf of your class.

If you have a credit card, you may place your donation online at <a href="https://www.nationalmssociety.org/donate/donate.asp">https://www.nationalmssociety.org/donate/donate.asp</a>. Otherwise, donations may be sent to:

National Multiple Sclerosis Society - Lone Star Chapter 8111 North Stadium Drive Houston, Texas 77054

If you restrict your donation to the National MS Society's targeted research campaign, 100% of your money will be directed to fund the latest research to find a cure for MS.

For the story of Ian Parberry's experience with Multiple Sclerosis, see <a href="http://www.thirdhemisphere.com/ms">http://www.thirdhemisphere.com/ms</a>.

### PITMAN PUBLISHING 128 Long Acre, London WC2E 9AN

© Ian Parberry 1987

First published 1987

Available in the Western Hemisphere from John Wiley & Sons, Inc. 605 Third Avenue, New York, NY 10158

ISSN 0268-7534

### **British Library Cataloguing in Publication Data**

Parberry, Ian

Parallel complexity theory.—(Research notes in theoretical computer science. ISSN 0268-7534). 1. Parallel programming (Computer science)

I. Title II. Series

004'.35

**QA76.6**

ISBN 0-273-08783-5

#### Library of Congress Cataloging in Publication Data

Parberry, Ian.

Parallel complexity theory/Ian Parberry.

p. cm.—(Research notes in theoretical computer science.

ISSN 0268-7534)

Bibliography: p.

Includes index.

ISBN 0-470-20931-3 (Wiley): 22.95 (est.)

1. Computational complexity. 2. Parallel processing (Electronic computers) I. Title. II. Series.

1987 QA267.P37 004'.35-dc19

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording and/or otherwise, without the prior written permission of the publishers. This book may not be lent, resold, hired out or otherwise disposed of by way of trade in any form of binding or cover other than that in which it is published, without the prior consent of the publishers.

Reproduced and printed by photolithography in Great Britain by Biddles Ltd, Guildford

### Foreword

Research in theoretical computer science has experienced tremendous growth both in the depth to which older theories have been pursued and also in the number of new problem areas that have arisen. While theoretical computer science is mathematical in nature, its goals include the development of an understanding of the nature of computation as well as the solution of specific problems that arise in the practice of computing.

The purpose of this series of monographs is to make available to the professional community expositions of topics that play an important role in theoretical computer science or that provide bridges with other aspects of computer science and with aspects of mathematics. The scope of the series may be considered to be that represented by the leading journals in the field. The editors intend that the scope will expand as the field grows and welcome submissions from all of those interested in theoretical computer science.

Ronald V. Book Main Editor

## Contents

| Chapter 1: | Introduction                             | 1  |

|------------|------------------------------------------|----|

| Chapter 2: | Combinational Circuits                   | 4  |

| 2.1.       | Sorting Networks                         | 4  |

| 2.2.       | Batcher's Sorting Networks               | 9  |

| 2.3.       | Waksman's Permutation Network            | 15 |

| 2.4.       | Parallel Prefix Computation              | 17 |

| 2.5.       | Exercises                                | 19 |

| Chapter 3: | Designing a Parallel Machine Model       | 21 |

| 3.1.       | The Basic Model                          | 22 |

| 3.2.       | The Unit-Cost Measure of Time            | 27 |

| 3.3.       | The Assignment of Programs to Processors | 29 |

| 3.4.       | Processor Activation                     | 32 |

| 3.5.       | Exercises.                               | 37 |

| Chapter 4: | Variants of the Model                    | 39 |

| 4.1.       | A Fixed-Structure Model                  | 39 |

| 4.2.       | Shared Memory Machines                   | 43 |

| 4.3.       | A Practical Model                        | 46 |

| 4.4.       | Exercises                                | 49 |

| Chapter 5: | Space and Parallel Time                  | 50 |

| 5.1.       | Small-Space Sequential Computations      | 50 |

| 5.2.       | Log-Space Completeness                   | 54 |

| 5.3.       | The Circuit-Value Problem                | 56 |

| 5.4.       | The Parallel Computation Thesis          | 62 |

| 5.5.       | Exercises                                | 68 |

| Chapter 6: P  | arallel Computation with Shared-Memory Machines | 70  |

|---------------|-------------------------------------------------|-----|

| 6.1.          | Some Upper-Bounds                               | 70  |

| 6.2.          | Simulation of Sequential Machines               | 76  |

| 6.3.          | A Lower-Bound Without Simultaneous Writes       | 80  |

| 6.4.          | A Lower-Bound With Simultaneous Writes          | 85  |

| 6.5.          | Exercises                                       | 87  |

| Chapter 7: P  | rogramming Techniques for Feasible Networks     | 89  |

| 7.1.          | Interconnection Patterns and Programming Tools  | 90  |

| 7.2.          | Recurrent Interconnection Patterns              | 94  |

| 7.3.          | Some Useful Algorithms                          | 101 |

| 7.4.          | Reducing the Number of Processors               | 105 |

| 7.5.          | Exercises                                       | 111 |

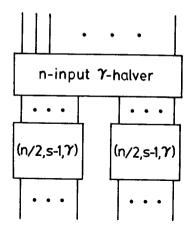

| Chapter 8: T  | he AKS Sorting Network                          | 113 |

| 8.1.          | Halvers and Nearsorters                         | 113 |

| 8.2.          | An Abstract Sorting Algorithm                   | 118 |

| 8.3.          | The Correctness Proof                           | 123 |

| 8.4.          | Exercises                                       | 130 |

| Chapter 9: Si | multaneous Resource Bounds                      | 132 |

| 9.1.          | A General Simulation Theorem                    | 132 |

| 9.2.          | A Universal Parallel Machine                    | 137 |

| 9.3.          | A Hardware Measure                              | 140 |

| 9.4.          | Circuits and Turing Machines                    | 144 |

| 9.5.          | Exercises                                       | 148 |

| Chapter 10: l | More on Universal Machines                      | 149 |

| 10.1.         | A Restricted Universal Machine                  | 149 |

| 10.2.         | Some Lower-Bounds                               | 153 |

| 10.3.         | A Non-Literal Simulation                        | 157 |

| 10.4.         | Oblivious Simulations                           | 159 |

| 10.5.         | Exercises                                       | 165 |

| Chapter 11: Unbounded Fan-in Parallelism |                                   | 166 |

|------------------------------------------|-----------------------------------|-----|

| 11.1.                                    | Unbounded Fan-in Circuits         | 167 |

| 11.2.                                    | Alternating Turing Machines       | 169 |

| 11.3.                                    | A New Parallel Computation Thesis | 172 |

| 11.4.                                    | Exercises                         | 177 |

| Chapter 12: Conclusion                   |                                   |     |

| References                               |                                   | 182 |

| Index                                    |                                   | 192 |

### Preface

Parallel complexity theory, the study of resource-bounded parallel computation, is surely one of the fastest-growing areas of theoretical Computer Science. In the light of this, it would be foolish to attempt an encyclopedic coverage of the field. However, it is the belief of the author that its foundations are becoming increasingly clear and well-defined. This Monograph is an attempt to present these foundations in a unified and coherent manner.

The material contained herein is aimed at advanced Graduate students or researchers in theoretical Computer Science who wish to gain an insight into parallel complexity theory. It is assumed that the reader has (in addition to a certain level of mathematical maturity) a general knowledge of Computer Science, and familiarity with automata theory, formal languages, complexity theory and analysis of algorithms. The interested reader may wish to augment his or her knowledge with books by Goldschlager and Lister [47], Hopcroft and Ullman [57], Garey and Johnson [39] and Aho, Hopcroft and Ullman [3].

This Monograph contains some of results that the author feels are fundamental, important, or exceptionally beautiful. The reader is free to make his or her own judgements. Lack of space and the current dynamic nature of the field prevent coverage of much recent material. In particular, results that are probabilistic in nature (both probabilistic proofs and results that concern probabilistic computations) have in general been avoided. This Monograph could not hope to do justice to so large and complicated a topic in the limited space available. There are sufficient results in probabilistic complexity theory to warrant a book devoted entirely to that subject.

The main part of this Monograph consists of twelve chapters. Chapter 1, the Introduction, sets the scene for the remainder of the work by elucidating our aims and motivation. Chapter 2 examines some early work in the field including sorting networks, permutation networks and the parallel prefix problem. Chapters 3 and 4 develop a parallel machine model that we will use throughout the remainder of the Monograph. Chapter 5 examines the parallel computation thesis, which is an attempt to characterize time-bounded parallel computation in

terms of space-bounded sequential computation. In Chapter 6 we explore the computational power of our machine model by providing upper and lower-bounds for some problems of interest. Chapter 7 contains some elementary results concerning a restricted variant of our machine model. Chapter 8 deals with the asymptotically optimal sorting network of Ajtai, Komlós and Szemerédi [5,6]. The results of Chapters 7 and 8 will be used in Chapter 9 to provide a restricted network which is universal for the general model with a modest increase in resources. Chapter 9 also considers the extended parallel computation thesis, an attempt to characterize time and hardware-bounded parallel computation. Chapter 10 is devoted to a more detailed discussion of universal parallel machines, whilst Chapter 11 covers unbounded fan-in parallelism and provides a new parallel computation thesis which operates in that framework. Finally, Chapter 12 is the Conclusion, which attempts to summarize and put into perspective the results of the previous ten chapters.

This Monograph has grown, under the encouragement of Ron Book, from the author's Doctoral Dissertation [91], which was supervised by M. S. Paterson. The preliminary notes were used for a Graduate-level course on parallel complexity theory at the Pennsylvania State University in 1986 and 1987. Students were required to complete homework problems plus a fairly substantial project (one of the choices for the latter being a summary of one of the papers from recent conference proceedings). With this in mind, some problems are provided at the end of most chapters. Naturally, some chapters are a more fruitful source of problems than others. None of the problems are particularly difficult, the most intransigent requiring the work of perhaps a few hours. No indication of difficulty is provided, since such qualitative judgements are usually unreliable. In the interests of fostering originality, no solutions are given. An attempt has been made to lead the reader to the threshold of the solution during the relevant chapter. If solutions have appeared elsewhere in print, they are either difficult to obtain or are substantially more complicated or more general than necessary. Students requiring inspiration will no doubt consult them despite these difficulties.

Many people have directly or indirectly contributed to the ideas contained in this Monograph. The author is particularly indebted to Les Goldschlager, Friedhelm Meyer auf der Heide, Mike Paterson, Nick Pippenger, Walter Ruzzo, Georg Schnitger, Janos Simon and Hans-Ulrich Simon for numerous discussions, either in-person or by correspondence. The author is also grateful to students,

particularly Joe Niederberger and Eric Mettala, who have offered helpful suggestions and pointed out minor errors in the manuscript. The author would particularly like to thank an anonymous referee, whose careful reading of, and thoughtful comments on a rough draft of this manuscript were greatly appreciated.

Ian Parberry, University Park, Pennsylvania, U.S.A. May, 1987. To my parents and to Virginia,

for putting up with me during the two most difficult periods of my life: growing up and writing this book, respectively.

### 1 Introduction

As recently as 1980, Schwartz [112] complained of an apparent lack of theoretical results concerning the computational complexity of parallel or concurrent algorithms.

"In the serial case, the design of algorithms has come to be illuminated by a growing body of theoretical knowledge concerning the ultimate limits of algorithm performance.... Until a like body of theoretical knowledge has been developed for highly concurrent algorithms, we will have little basis for judging the extent to which a given concurrent approach can be improved."

Two of the most important and fundamental papers in the field of parallel complexity theory (those of Goldschlager [41,45], and Pippenger [102]) had already appeared by the time Schwartz's paper reached publication. Since then, the flow of results has increased from a trickle to a steady stream, and is now threatening to become a flood. Today, parallel complexity theory must be ranked as one of the fastest-growing fields of theoretical Computer Science.

A theoretical treatment of parallel computation is an attempt to formalize the intuitive concept of a "parallel computer" based on practical experience or reasonable expectations. Amongst the questions which should be addressed by such a formal exposition are the following:

- What do we mean by parallel computation?

- What constitutes a good model of a parallel computer?

- What are the resources of interest, and how should they be defined?

- How should we express parallel algorithms?

- What kind of problems lend themselves to a fast solution on a parallel computer?

- What resources do we need to solve a given interesting problem in parallel?

The latter question appears to be the most popular, judging by sheer volume of contributions (for example, consult [105,127] and the references contained

therein). In contrast, relatively little attention has been paid to the first four questions, which has resulted in a proliferation of parallel machine models in the current literature. Even the most popular model, the shared-memory machine (consisting of a collection of RAMs communicating via a shared memory, see, for example, [33,45]) has many variants.

Intuitively, a parallel machine should consist of a collection of processors which in some way co-operate in order to compute a result. Obviously there are many ways of formalizing this intuition. Compare the SIMDAG of Goldschlager [45] to the model of Galil and Paul [38]. The processors of the former are RAMs; the latter allow processors which range from RAMs to finite-state machines. Lev, Pippenger and Valiant [74] use RACs. Goldschlager has almost identical processors which are all started simultaneously at the start of the computation, and communicate via a shared memory. Galil and Paul have "similar" processors which start up at run-time, and communicate via direct processor-to-processor links. Some of the more obvious variations on these models include the instruction-set (for example, should multiplication be allowed?), and memory access conflicts (should multiple attempts to write to a shared memory location be allowed as in [45], or should even multiple reads be disallowed, as in [74,118]?). Some of these differences are cosmetic in nature, while others are more crucial.

We will choose a model which consists of a network of interconnected RAMs; each RAM can in one step perform an internal computation, or read from or write to a register belonging to one of its neighbours. We believe that the network paradigm is fundamental to the understanding of parallel computation. One attraction is the fact that it possesses a certain theoretical elegance. The network model has the advantage of encompassing a number of popular machine models, for example, a shared-memory machine (see Section 4.2) is just a network where all processors can communicate with a single distinguished processor and no other, and that distinguished processor remains idle throughout the computation. The number of extant papers which use the shared-memory model attest to its ease of programming, and its usefulness as a tool for proving and communicating theoretical results. It is widely accepted, however, that the shared-memory model is not a viable architecture. By placing restrictions on our network model, it is possible to define a practical variant in a natural and elegant fashion.

The aim of this Monograph, then, is to shed some light on the nature of parallel computation. We shall do this by presenting a unified theory of parallel computation based on a network model. We shall demonstrate its utility by

providing some fairly concise and elegant proofs of results from the current literature (which will occasionally lead to improved resource bounds or more general theorems). We will also attempt to provide answers to the questions posed at the start of this Introduction.

It should be noted that this is a theoretical treatment of parallel computation, and as such is based upon a number of assumptions which are widely accepted amongst workers in the field of parallel complexity theory. Although our model is synchronous (in the sense that the instruction-cycles of the processors are synchronized), we will see in Section 4.3 that this is not an important restriction. Synchronous models are far easier to deal with than asynchronous ones. We assume that inter-processor communications can take place within a single instruction-cycle. In the real world, this assumption is unlikely to be true for large numbers of processors; a complexity theory based on this observation will differ quite radically from ours [111]. However, we feel fairly safe in making the assumption for networks consisting of a small number (say in the millions) of fairly large processors (about the size of a microprocessor), even though it is unlikely to hold for, say, individual gates in a VLSI chip.

Finally, the reader should note that throughout this work, all logarithms are to base 2, N denotes the set of non-negative integers, Z the set of integers, and R the set of real numbers. If  $c \in N$ ,  $d \in Z$ , then  $d \mod c$  is defined to be the unique integer  $a \in N$  such that  $0 \le a < c$  and there exists  $b \in Z$  such that a+bc = d. For those unfamiliar with the "order" notation, we provide the following reminder. Let  $f,g:N \to R^+$  (where  $R^+$  denotes the set of positive real numbers). We say that:

- 1. f(n) = O(g(n)) if there exists  $c \in \mathbb{R}^+$ ,  $n_0 \in \mathbb{N}$  such that for all  $n \ge n_0$ ,  $f(n) \le c g(n)$ .

- 2.  $f(n) = \Omega(g(n))$  if there exists  $c \in \mathbb{R}^+$ ,  $n_0 \in \mathbb{N}$  such that for all  $n \ge n_0$ ,  $f(n) \ge c g(n)$ .

- 3.  $f(n) = \Theta(g(n))$  if f(n) = O(g(n)) and  $f(n) = \Omega(g(n))$ .

- $4. \quad f(n)=o(g(n)) \text{ if } \lim_{n\to\infty}\frac{f(n)}{g(n)}=0.$

### 2 Combinational Circuits

Early research in parallel complexity theory focussed on combinational circuits, that is, circuits without feedback loops. In this model, we are given as "basic units" a collection of gates which can compute certain useful functions on a fixed number of inputs in one time-unit. Our aim is to construct a circuit which is efficient in both parallel time and hardware to compute a desirable function on n inputs. We are allowed to wire the gates together in an arbitrary manner without feedback loops. We use the depth and size of the circuit as a measure of parallel time and hardware respectively. The depth of a combinational circuit is the maximum number of gates on a path from an input to an output. The size is the number of gates used.

The first problem that we will tackle is that of sorting n values. The "basic units", called *comparators*, are gates which can sort two inputs. The circuits are further constrained in a manner more fully described in Section 2.1. In that section we also prove some useful preliminary results on sorting networks. In Section 2.2 we meet sorting networks based on Batcher's odd-even merge and bitonic sorting networks, with depth  $O(\log^2 n)$  and size  $O(n \log^2 n)$ . Section 2.3 investigates a slightly easier problem, that of performing fixed permutations using basic units called *switches*. We meet Waksman's permutation network, which has logarithmic depth and log-linear size. Finally, Section 2.4 presents the parallel prefix circuit of Fischer and Ladner, of logarithmic depth and linear size.

### 2.1. Sorting Networks

One of the early investigations into parallel complexity theory concerned a variant of the sorting problem, dubbed the *Bose-Nelson sorting problem* by Floyd and Knuth [31], after Bose and Nelson [17]. We are given a basic unit of hardware called a *comparator*. A comparator takes two integers as input, and outputs them in ascending order. A *comparator network* is a circuit built from comparators according to the following constraints.

- 1. The values to be sorted are treated as atomic units. They may neither be divided nor duplicated.

- 2. The values travel in n channels, which we will represent in our diagrams as vertical lines. The inputs will be presented at the top of the network, and will appear in some permuted order at the bottom.

- 3. The network is divided vertically into a finite number of levels, which are numbered consecutively, starting at 0. The 0<sup>th</sup> level consists of the inputs. Each of the subsequent levels contains one or more comparators. Each comparator is placed on two channels. At most one comparator is placed on any channel at any particular level. We will depict a comparator using a horizontal line between the two channels, with heavy dots emphasizing the connection-points (see Figure 2.1.1).

We will number the channels 1 through n, in ascending order from left to right. We will say that channel i carries value v at level j on input  $x_1,...,x_n$  if either

- (i) j = 0 and  $x_i = v$ , or

- (ii) j > 0, there is no comparator on channel i at level j, and channel i carries value v at level j-1, or

- (iii) j > 0, there is a comparator between channels i and k at level j, k < i, channel i carries value  $v_i$  at level j-1, channel k carries value  $v_k$  at level j-1, and  $v = \max(v_i, v_k)$ , or

- (iv) j > 0, there is a comparator between channels i and k at level j, k > i, channel i carries value  $v_i$  at level j-1, channel k carries value  $v_k$  at level j-1, and  $v = \min(v_i, v_k)$ .

The output of the network consists of the n values carried by the channels at the final level, in left-to-right order. If they are always in ascending order from left-to-right, the network is called a *sorting network*.

Figure 2.1.1 A comparator.

Each level of a comparator network consists of a set of independent comparisons which may be performed in parallel. The number of levels is thus a reasonable measure of parallel time. We will call this the depth of the network. We are also interested in the size of the network, that is, the number of comparators used. For example, consider the following algorithm for sorting four values. In parallel, compare the first value with the second, and the third with the fourth. This is the first level of the network. Clearly the minimum of the two minima is the smallest of the four values, and the maximum of the two maxima is the largest. This is the second level of the network. However, at that point we know nothing of the relative order of the remaining two values. The third level of the network compares them. This gives us the depth-3, size-5 sorting network in Figure 2.1.2.

Figure 2.1.2 A sorting network with 4 inputs, of size 5 and depth 3.

We have chosen to build our network using comparators which send the smallest value to the left, and the largest to the right. Let us call these *min-max* comparators, as opposed to *max-min* comparators, which send the largest to the left and the smallest to the right. We have not lost anything by restricting outselves to min-max comparators:

Theorem 2.1.1 (Floyd-Knuth) For every sorting network built from a mixture of max-min and min-max comparators there is a sorting network with the same size and depth built purely from min-max comparators.

**Proof.** Suppose C is a sorting network built from min-max and max-min comparators, of depth d and size s. Suppose we represent each comparator as a 3-tuple  $\langle a,b,c \rangle$ , where a denotes its level number, and b and c the channels on which its min-output and max-output emerge respectively. Note that a min-max comparator will have b < c, while a max-min comparator will have b > c.

Let  $\Pi$  be a permutation of the set  $\{1,...,n\}$ , that is,  $\Pi:\{1,...,n\} \to \{1,...,n\}$  and is one-to-one and onto. Let (i,j) denote the permutation  $\Pi$  such that  $\Pi(i) = j$ ,  $\Pi(j) = i$  and  $\Pi(k) = k$  for  $k \neq i,j$ . Define the product of two permutations  $\Pi = \Pi_1\Pi_2$  by  $\Pi(i) = \Pi_1(\Pi_2(i))$  for  $i \in \{1,...,n\}$ . Define a  $\Pi$ -sorter to be a comparator network whose outputs are in sorted order after application of  $\Pi$  to the channels below the final level. Thus, in this new terminology, a sorting network is an I-sorter, where I denotes the identity permutation.

We will represent a comparator network as a list of 3-tuples, each of which represents a comparator. We will insist that the list is in ascending order on the first index, that is, comparators on the lowest-numbered levels appear first. Let  $C = \langle C_1, C_2, ..., C_s \rangle$ , where  $C_i = \langle a_i, b_i, c_i \rangle$  for  $1 \leq i < s$ , and  $a_i \leq a_{i+1}$  for  $1 \leq i < s$ . Consider the following algorithm:

```

\begin{split} \text{L}:=& \text{C} \\ \Pi:=& I \\ \text{for } i:=& 1 \text{ to s do} \\ \text{if } b_i > c_i \text{ then} \\ \text{for } j:=& i \text{ to s do} \\ \text{Consider } L_j = & < a_j, b_j, c_j > \\ \text{if } b_j = b_i \text{ then } b_j := c_i \\ \text{else if } b_j = c_i \text{ then } b_j := b_i \\ \text{if } c_j = b_i \text{ then } c_j := c_i \\ \text{else if } c_j = c_i \text{ then } c_j := b_i \\ \Pi:=& \Pi \left(b_i, c_i\right) \end{split}

```

Claim 1. After the i<sup>th</sup> iteration of the outer for-loop, L is a  $\Pi$ -sorter, for  $0 \le i \le s$ .

**Proof.** The result follows by induction on i. The hypothesis is true for i = 0, since immediately before the first iteration, L = C, and is thus an *I*-sorter. Now suppose that the hypothesis is true after the  $(i-1)^{st}$  iteration. There are two cases to consider.

Case 1.  $b_i < c_i$ . No change is made to either L or  $\Pi$ , so L remains a  $\Pi$ -sorter by the induction hypothesis.

Case 2.  $b_i > c_i$ . The effect of the algorithm is to "swap" channels  $b_i$  and  $c_i$  "below" level i. Thus by the induction hypothesis, the outputs are  $\Pi$ -sorted, since  $\Pi$  is modified to swap the outputs on those channels back into sorted order.

Claim 2. After the i<sup>th</sup> iteration of the outer for-loop,  $\{L_1,...,L_i\}$  are all min-max comparators.

**Proof.** The proof follows easily by induction on i.  $\Box$

Claim 3. On termination of the algorithm,  $\Pi = I$ .

**Proof.** When the algorithm has terminated, L is a  $\Pi$ -sorter for some  $\Pi$  (by Claim 1) built from min-max comparators (by Claim 2). Suppose we give L a sequence of integers which are already sorted in ascending order. Since L is built from min-max comparators, no swapping is done; the values stay on their respective channels. Thus the values are still in ascending order when they reach the outputs. Furthermore, they are still sorted after application of  $\Pi$ , which implies  $\Pi = I$ .  $\square$

Thus by Claims 1, 2 and 3, on termination of the algorithm, L is a sorting network built from min-max comparators. It is easy to prove by induction that L has depth d and size s.  $\square$

An obvious method for proving that an n-input comparator network sorts is to try all n! different permutations of n distinct numbers as inputs to the network. However, slightly fewer trials suffice. The following Theorem is attributed to Bouricius by Knuth [65].

Theorem 2.1.2 (The Zero-One Principle). An n-input comparator network is a sorting network iff it sorts all sequences of n zeros and ones.

**Proof.** Clearly if a comparator network sorts, then it will correctly sort all sequences of zeros and ones. Conversely, suppose we have a comparison network which sorts all sequences of zeros and ones. Suppose  $\alpha \in \mathbb{R}$  is a constant. Define  $h_{\alpha}: \mathbb{Z} \to \mathbb{Z}$  as follows:

$$h_{\alpha}(x) = \begin{cases} 1 & \text{if } x \ge \alpha \\ 0 & \text{otherwise} \end{cases}$$

Claim. For  $j \ge 0$ , if for inputs  $x_1, x_2, ..., x_n$  a channel carries the value  $\beta$  at level j, then for inputs  $h_{\alpha}(x_1), h_{\alpha}(x_2), ..., h_{\alpha}(x_n)$  it carries the value  $h_{\alpha}(\beta)$  at level j.

**Proof.** The result follows by induction on j. The hypothesis is trivially true for j = 0. Now suppose j > 0. Consider channel i, which has value  $\beta$  at level j on input  $x_1,...,x_n$ . We will write  $v(i,j) = \beta$ . We will also write  $v_{\alpha}(i,j)$  for the value that channel i carries at level j on input  $h_{\alpha}(x_1),...,h_{\alpha}(x_n)$ . If there is no

comparator on channel i at level j, then  $v_{\alpha}(i,j) = h_{\alpha}(\beta)$  by the induction hypothesis. Suppose there is a comparator between channels i and k at level j. There are two cases to consider.

Case 1. i < k. Suppose  $v(i,j-1) = \beta_i$ ,  $v(k,j-1) = \beta_k$ . Then  $\beta = \min(\beta_i,\beta_k)$ . Thus:

$$\begin{split} \mathbf{v}_{\alpha}(\mathbf{i}) &= \min(\mathbf{v}_{\alpha}(\mathbf{i},\mathbf{j}-1), \mathbf{v}_{\alpha}(\mathbf{k},\mathbf{j}-1)) \\ &= \min(\mathbf{h}_{\alpha}(\beta_{\mathbf{i}}), \mathbf{h}_{\alpha}(\beta_{\mathbf{k}})) \qquad \text{(by the induction hypothesis)} \\ &= \mathbf{h}_{\alpha}(\min(\beta_{\mathbf{i}},\beta_{\mathbf{k}})) \qquad \text{(by the definition of $\mathbf{h}_{\alpha}$)} \\ &= \mathbf{h}_{\alpha}(\beta) \end{split}$$

Case 2. k < i. Similar to Case 1, replacing "min" by "max". □

Suppose we have an n-input comparator network C which sorts all sequences of zeros and ones. Suppose we give it inputs  $x_1,...,x_n$ . Let the outputs, in left-to-right order, be  $y_1,...,y_n$ . For a contradiction, suppose that they are not in ascending order, in particular that  $y_i > y_{i+1}$  for some  $1 \le i < n$ . By the above Claim, when C is given the inputs  $h_{\alpha}(x_1),...,h_{\alpha}(x_n)$ , its outputs are, in left-to-right order,  $h_{\alpha}(y_1),...,h_{\alpha}(y_n)$ . Choose  $\alpha = (y_i + y_{i+1})/2$ . Then  $h_{\alpha}(y_i) = 1$  and  $h_{\alpha}(y_{i+1}) = 0$ , which contradicts the fact that C sorts all sequences of zeros and ones. Therefore  $y_1,...,y_n$  must be in sorted order, and so C is a sorting network.  $\square$

#### 4.2. Batcher's Sorting Networks

The sorting networks in this section are due to Batcher [10]. Since we are mainly interested in the asymptotic depth and size complexity of sorting networks, it is sufficient to consider sorting n inputs where n is a power of 2 (since if we wish to sort an arbitrary number of values, we can add enough large "dummy" elements to fill out n to a power of 2; this increases the number of inputs, and hence the size and depth, by at most a small constant multiple). This has the added benefit of simplifying the proofs. More detailed proofs for general n can be found in Knuth [65]. Let p be a power of 2. Consider the following recursive description of a network to merge two sorted sequences  $a = \langle a_1, ..., a_p \rangle$  and  $b = \langle b_1, ..., b_p \rangle$ . If p = 1 then the network consists of a single comparator. If p > 1 then recursively merge the odd-numbered elements of a with the odd-

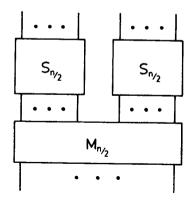

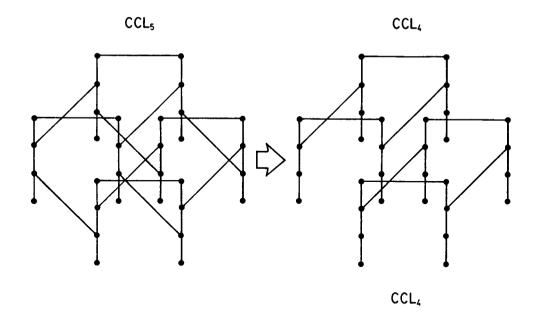

numbered elements of b, merge the even-numbered elements of a with the even-numbered elements of b, then insert a final level of comparators between channel 2i and channel 2i+1,  $1 \le i < n/2$ . Figure 2.2.1 shows the construction of  $M_p$ , a comparator network to merge two sorted p-sequences, from two copies of  $M_{p/2}$  according to this description. The network thus obtained is called the *odd-even merging network*.

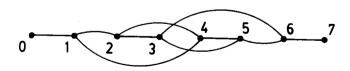

Figure 2.2.1 Batcher's odd-even merging network.

Theorem 2.2.1 Mp will merge two sorted sequences of length p.

**Proof.** The proof will follow by induction on p. The hypothesis is clearly true for p=1. Now suppose that the two recursive sub-networks merge correctly. We will make use of the fact that the Zero-One Principle holds for merging networks (see Exercise 2.1). Let  $a=\langle a_1,...,a_p\rangle$  and  $b=\langle b_1,...,b_p\rangle$  denote the two sorted input sequences,  $c=\langle c_1,...,c_p\rangle$  denote the output from the left-hand ("odd") recursive sub-network,  $d=\langle d_1,...,d_p\rangle$  denote the output from the right-hand ("even") recursive sub-network,  $e=\langle e_1,...,e_{2p}\rangle$  denote the sequence of values immediately before the final level of comparators, and  $f=\langle f_1,...,f_{2p}\rangle$  denote the output, in left-to-right order (see Figure 2.2.1).

Suppose that a consists of g zeros followed by p-g ones, and that b consists of h zeros followed by p-h ones. Then, by the induction hypothesis, c consists of  $\lceil g/2 \rceil + \lceil h/2 \rceil$  zeros followed by p- $\lceil g/2 \rceil - \lceil h/2 \rceil$  ones, and d consists of  $\lfloor g/2 \rfloor + \lfloor h/2 \rfloor$  zeros followed by p- $\lfloor g/2 \rfloor - \lfloor h/2 \rfloor$  ones. Thus c has either the same number, one more, or two more zeros than d. Therefore, noting that  $e = \langle c_1, d_1, c_2, d_2, ..., c_p, d_p \rangle$ , there are three cases to consider:

Case 1. c has the same number of zeros as d. If g=h=0 then the output is sorted. Otherwise e is of the form e=<0,0,...0,1,0,1,1,...,1>, more specifically,  $e_i=0$  for  $1\leq i\leq g+h-1$ ,  $e_{g+h}=1$ ,  $e_{g+h+1}=0$  and  $e_i=1$  for  $g+h+1< i\leq n$ . Since g=h, g+h is even, and therefore there is a comparator between  $e_{g+h}$  and  $e_{g+h+1}$  in the final level. This ensures that f is in sorted order.

Case 2. c has one more zero than d. Then e is already sorted, which implies that f is sorted.

Case 3. c has two more zeros than d. Then, as in Case 2, e is already sorted, which implies that f is sorted.

In each case, the final output is sorted. Therefore, the merger correctly merges all sequences of zeros and ones, which by the Zero-One Principle implies that it merges all sequences of integers.

Let d(p) be the depth, and s(p) the size of an odd-even merging network which merges two sorted sequences of length p. Then d(1) = 1, and for p > 1, d(p) = d(p/2)+1. By induction on p,  $d(p) = \log p + 1$ . Also, s(1) = 1, and for p > 1, s(p) = 2s(p/2)+p-1. By induction on p,  $s(p) = p \log p + 1$ .

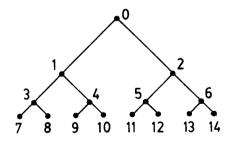

The following is the recursive description of an n-input sorting network, called the *odd-even sorting network*. If n=1, then the network is empty. If n>1, sort the first half of the values recursively, sort the second half of the values recursively, and then merge the two sorted sequences using an odd-even merging network. Figure 2.2.2 shows the construction of  $S_n$ , a network for sorting n inputs, from two copies of  $S_{n/2}$  and one copy of  $M_{n/2}$  according to this description.

The correctness of the odd-even sorting network is easily proved by induction. Let D(p) be the depth, and S(p) the size of an odd-even sorting network with n inputs. Then D(1) = 0 and for n > 1,

$$D(n) = D(n/2) + d(n/2)$$

$$= D(n/2) + \log n.$$

Figure 2.2.2 Batcher's odd-even sorting network.

Therefore, by induction,

$$D(n) = \frac{1}{2}(\log n)(\log n + 1).$$

Also, S(1) = 0 and for n > 1,

$$S(n) = 2 S(n/2) + s(n/2)$$

$$= 2 S(n/2) + \frac{n}{2} (\log n - 1) + 1.$$

Therefore, by induction.

$$S(n) = \frac{n}{4} (\log n) (\log n - 1) + n - 1.$$

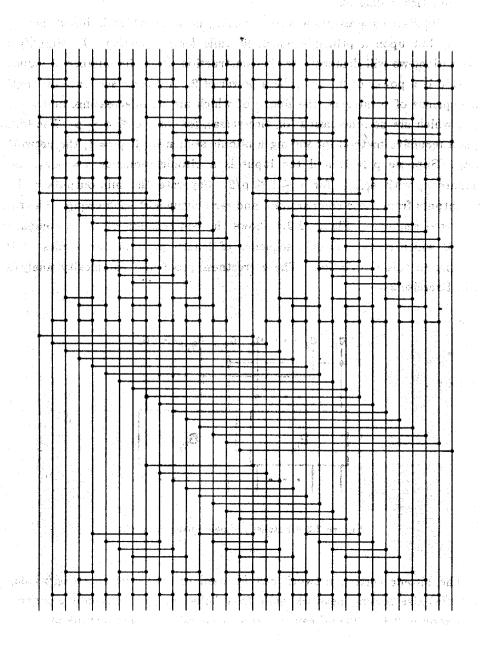

Figure 2.2.3 shows an odd-even sorting network with 32 inputs, of depth 15 and size 191. The recursive structure of this network is immediately apparent.

Thus we see that it is possible to sort n inputs in depth O(log<sup>2</sup>n) and size O(n log<sup>2</sup>n), with very small constant multiples in the resource bounds (certainly less than 1 for large enough n, even when n is not a power of 2). Recently, Ajtai, Komlós and Szemerédi [5,6] demonstrated that depth O(log n) and size O(n log n) is possible. This new network (which we will describe in more detail in Chapter 8) is of great interest theoretically because it is asymptotically optimal in both size and depth (see Exercise 2.2). However, since the constant multiples in the depth and size bounds are so large, the odd-even sorting network outperforms it

Figure 2.2.3 An odd-even sorting network with 32 inputs.

for all practical values of n.

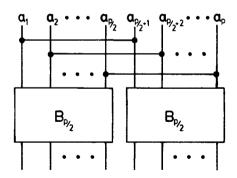

In [10] Batcher presents a second sorting network which is based, not upon merging, but upon a principle which he calls bitonic sorting. To simplify the presentation, we will demonstrate the construction when the number of values to be sorted is a power of 2. Let p be a power of 2. A bitonic sequence of length p is a sequence of p integers, the first q of which are non-decreasing, and the last p-q of which are non-increasing (or vice-versa), for some  $0 \le q \le p$ . The following is a recursive method for sorting a bitonic sequence. If p = 1, the network is empty. Suppose p > 1, and the input is a bitonic sequence  $a = \langle a_1, ..., a_p \rangle$ . Compare  $a_i$  with  $a_{i+p/2}$ , for  $1 \le i \le p/2$ . Separate the min-outputs and the max-outputs from these comparators, and recursively sort each group. The result is a sorted sequence. Figure 2.2.4 shows the construction of  $B_p$ , a comparator network which sorts a bitonic sequence of length p, from two copies of  $B_{p/2}$  according to this description. The correctness proof and complexity analysis is left to Exercise 2.3.

Figure 2.2.4 Batcher's bitonic sorting network.

The bitonic sorting network can be used to construct an  $O(\log^2 n)$  depth,  $O(n \log^2 n)$  size sorting network built from min-max and max-min comparators (see Exercise 2.4). These can be converted to min-max comparators using Theorem 2.1.1. There is some confusion in the literature over the nomenclature "bitonic sorting network". We use it, as did Batcher, to denote a comparison network which sorts bitonic sequences. It has become popular to use it to

describe the sorting network which is constructed from bitonic sorters.

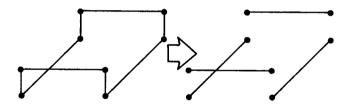

#### 2.3. Waksman's Permutation Network

Consider the problem of permuting n inputs. We will use a network similar to the comparator network defined in the previous section. Instead of comparators the basic building blocks will be *switches*. A switch, like a comparator, can either pass its two inputs directly to the outputs, or swap them. A comparator swaps if the right input is smaller than the left input. In contrast, a switch is subject to outside control. A switch can either be set to *on*, indicating that it is to swap its inputs, or *off* indicating that it is to pass the inputs through directly, unchanged in any way. A network built from switches according to the following constraints is called a *switching network*.

- 1. The values to be sorted are treated as atomic units. They may neither be divided nor duplicated.

- 2. The values travel in n channels, which we will in our diagrams represent by vertical lines. The inputs will be presented at the top of the network, and will appear in some permuted order at the bottom.

- 3. The channels are labelled 1 through n, in ascending order from left to right. The network is divided vertically into a finite number of levels, which are numbered consecutively, starting at 0. The 0<sup>th</sup> level consists of the inputs. Each of the subsequent levels contains one or more switches. Each switch is placed on two channels. At most one switch is placed on any channel at any particular level. We will depict a switch using a horizontal line between the two channels, with heavy dots emphasizing the end-points, in the same manner as we depicted comparators in the previous section.

We will say that channel i carries value v at level j on input  $x_1,...,x_n$  if either

- (i) j = 0 and  $x_i = v$ , or

- (ii) j > 0, there is no switch on channel i at level j, and channel i carries value v

at level j-1, or

- (iii) j > 0 and there is a switch on channel i at level j, that switch is "off" and channel i carries value v at level j-1, or

- (iv) j > 0 and there is a switch between channels i and k at level j, that switch is "on" and channel k carries value v at level j-1.

The output of the network consists of the n values carried by the channels at the final level, in left-to-right order. As with comparator networks, the depth of a

switching network is the number of levels, and the *size* is the number of switches. An n-input switching network is called a *permutation network* if, for every permutation  $\Pi$  on n objects, the switches of the network can be set in such a manner that the output of the network consists of the inputs whose positions have been permuted according to  $\Pi$ . That is, on input  $x_1,...,x_n$  the output of the network is  $x_{\Pi^{-1}(1)},...,x_{\Pi^{-1}(n)}$ .

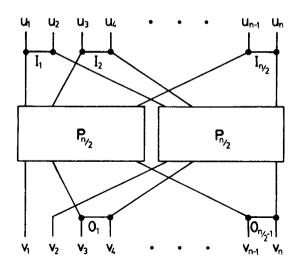

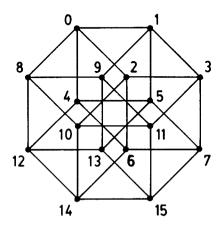

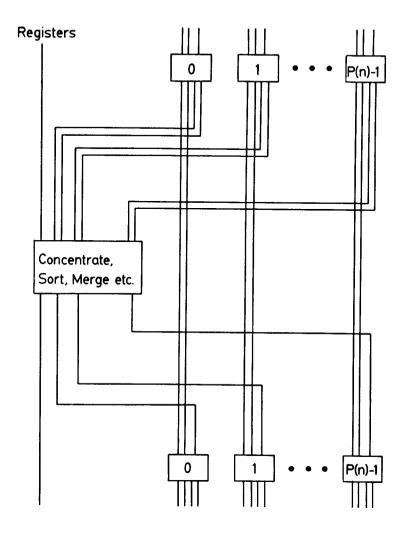

The following is the recursive description of a permutation network with n inputs, due to Waksman [131]. Suppose n is a power of 2. If n=1, then the network consists of a single channel with no switches. If n>1, place a level of switches between channel 2i-i and channel 2i,  $1 \le i \le n/2$ . Separately, take the left-outputs and right-outputs from these switches, and recursively permute them. Finally, place switches between channel 2i-1 and channel 2i, for  $2 \le i \le n/2$ . Figure 2.3.1 shows the construction of  $P_n$ , a switching network which permutes n inputs, from two copies of  $P_{n/2}$  according to this description.

Figure 2.3.1 Waksman's permutation network.

Theorem 2.3.1 The switches of Waksman's permutation network can be set to realize any permutation of n inputs.

**Proof.** The proof follows by induction on n. Suppose the inputs are  $u_1,...,u_n$ , and the outputs are  $v_1,...,v_n$ , and that we number the first layer of switches  $I_1,...,I_{n/2}$ , and the last layer of switches  $O_1,...,O_{\frac{n}{2}-1}$ . The induction hypothesis is

trivially true when n=1. Now suppose n>1. Take any permutation on n objects. Start with  $v_1$ . Set the switches of the left-hand copy of  $P_{n/2}$  to route it to the appropriate I-switch. Set that I-switch to route it to the appropriate input. Say that input is  $u_i$ . Now consider  $u_{i+(-1)^k}$ , the "partner" of  $u_i$  in switch I  $\{i/2\}$ . It has been routed to the right-hand copy of  $P_{n/2}$ . Set the switches of that sub-network to route it to the appropriate O-switch (or to  $v_2$ , if necessary). Set that O-switch to send it to the appropriate output. Continue this process, at each stage selecting the "partner" of the previously processed channel in the appropriate I-switch or O-switch. If the partner has already been chosen (or we end up at  $v_2$ ), start again from any other input or output value. Continue in this manner until all of the input-output routings have been made. By the induction hypothesis, the switches of the sub-networks can be set in such a manner that the appropriate sub-permutations are realized.  $\square$

Let D(n) denote the depth, and S(n) denote the size of Waksman's permutation network on n inputs. Then D(1) = 0, and for n > 1, D(n) = D(n/2) + 2. Therefore, by induction,  $D(n) = 2 \log n$ . Also, S(1) = 0, and for n > 1, S(n) = 2 S(n/2) + n-1. Therefore, by induction,  $S(n) = n \log n - n + 1$ . Since the lower-bounds of Exercise 2.2 hold equally well for permutation networks, these results are asymptotically optimal.

### 2.4. Parallel Prefix Computation

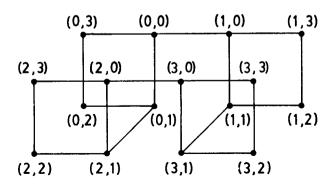

Suppose we have an "addition gate", which computes the sum of two inputs. It is easy to construct a combinational circuit with addition gates, of depth  $\lceil \log n \rceil$  and linear size, to sum n inputs (using a binary tree). However, suppose that we want a circuit with n inputs and n outputs, such that on input  $\langle x_1,...,x_n \rangle$  the output is  $\langle y_1,...,y_n \rangle$ , where for  $1 \leq i \leq n$ ,  $y_i = \sum_{j=1}^i x_j$ . This is called the parallel prefix problem. The obvious solution uses n trees, has logarithmic depth and quadratic size. However, it is possible to obtain logarithmic depth and linear size. The following is a recursive description of a parallel prefix circuit on n inputs, due to Fischer and Ladner [70].

Suppose n is a power of 2. On input  $\langle x_1,...,x_n \rangle$ , first compute  $x_i+x_{i+1}$  for each odd i,  $1 \le i \le n-1$ . Compute the prefix-sum of these values, using a subnetwork with n/2 inputs. The i<sup>th</sup> output of the sub-network becomes the (2i)<sup>th</sup>

Figure 2.4.1 The parallel prefix circuit of Fischer and Ladner.

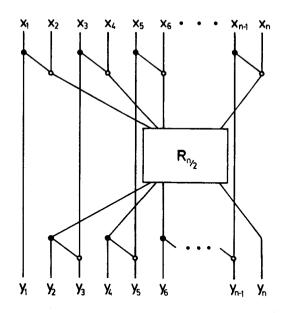

output of the network, for  $1 \le i \le n/2$ . The first output of the network is just  $x_1$ . The  $(2j-1)^{th}$  output of the network,  $2 \le j \le n/2$  consists of the  $j^{th}$  output of the sub-network added to  $x_{2j-1}$ . Figure 2.4.1 gives the recursive construction of an n-input parallel prefix circuit  $R_n$  from  $R_{n/2}$ , according to this description. In that diagram, solid dots denote fan-out, and circles denote addition gates.

The correctness of the construction can be readily verified by induction on n. Let D(n) denote the depth, and S(n) the size of an n-input parallel prefix circuit. Then D(1) = 0, and for n > 1, D(n) = D(n/2) + 2. Therefore, by induction,  $D(n) = 2 \log n$ . Also, S(1) = 0, and for n > 1, S(n) = S(n/2) + n-1. Therefore, by induction,  $S(n) = 2n-2-\log n$ . These bounds are easily seen to be asymptotically optimal.

### 2.5. Exercises

- 2.1 Prove that the Zero-One Principle (Theorem 2.1.2) holds equally well for merging networks. That is, a comparator network merges two sorted sequences of integers iff it merges two sorted sequences of zeros and ones.

- 2.2 Show that an n-input sorting or permutation network must have size at least  $n \log n o(n)$ . Show that an n-input sorting or permutation network must have depth at least  $2 \log n o(1)$ . (Hint: use Stirling's approximation).

- 2.3 Use the Zero-One Principle to prove the correctness of Batcher's bitonic sorting network. Analyze its size and depth.

- 2.4 Use Batcher's bitonic sorting network to construct a sorting network which will sort all input sequences, not just bitonic ones. Prove its correctness, and analyze its size and depth.

- 2.5 (Van Voorhis [130]). Let S(n) denote the minimum size of an n-input sorting network. Prove that  $S(n) \geq S(n-1) + \left\lceil \log_2 n \right\rceil$ .

We saw in Section 2.2 how to construct a sorting network using comparators. These are gates which input two integers, and output them in sorted order. Suppose that we also have 3-comparators. These are gates which input three integers, and output them in sorted order. In our diagrams, we will draw 3-comparators as horizontal lines, with three heavy dots denoting connections to the appropriate channels.

- 2.6 Prove that the Zero-One Principle (Theorem 2.1.2) still holds. That is, prove that a network built from comparators and 3-comparators sorts iff it can sort all sequences of zeros and ones.

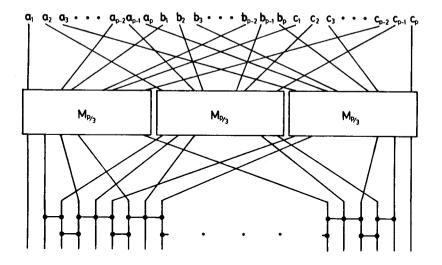

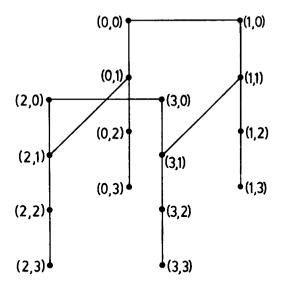

- 2.7 Prove, using the Zero-One Principle (see Exercise 2.6), that the following network  $M_p$  (adapted from Tseng and Lee [123]) will merge three sorted sequences of p integers, where p is a power of 3.  $M_1$  is just a single 3-comparator.  $M_p$  is constructed recursively from three copies of  $M_{p/3}$  as in Figure 2.5.1. We call this network the modulo-3 merging network. Show that its depth is  $2 \log_3 p + 1$ , and that it uses  $p \log_3 p + 1$  3-comparators and  $p \log_3 p + \frac{p-1}{2}$  2-comparators.

Figure 2.5.1 The modulo-3 merging network.

- 2.8 Use the merging network of Exercise 2.7 to construct a network for sorting n integers (where n is a power of 3) with depth  $\log_3^2$ n. How many 3-comparators and 2-comparators does your sorting network use?

- 2.9 Suppose we can build a gate which adds k numbers. Construct a circuit for finding the prefix-sum of n numbers with depth (2  $\lceil \log_k n \rceil$ ) and linear size.

## 3 Designing a Parallel Machine Model

In Chapter 2 we saw three primitive parallel machine models which were particularly suited to a limited type of computation. In this chapter we present a general parallel machine model and attempt to justify some of the decisions which contributed to its design. Informally, the model consists of a synchronous network of sequential processors, each of which have random-access to each other's memory. In the first section we give a more formal description, providing illustration by way of an example instruction-set. We define the major resources of interest: processors (the number of sequential processors used), time (number of instructions executed), degree (degree of the interconnection graph), space (number of registers required) and word-size (the size of those registers). In order to simplify the presentation of algorithms, we describe a high-level pseudo-programming language which we will use in subsequent chapters.

The second section is devoted to a discussion of our choice of a unit-cost measure of time. We choose to charge a single unit of time for each instruction executed, rather than charge according to some notion of "difficulty". This raises an interesting question: for which instruction-sets is this valid? It does not a priori seem reasonable to charge a single unit of time for complex instruction sets, but it is not obvious as to exactly where the line should be drawn. We shall see in subsequent chapters that the answer can be provided in several different ways.

Our basic networks have a single program for all processors. In the third section we justify this approach, comparing and contrasting it with the SIMD and MIMD machines of Flynn [32]. In a SIMD machine the processors have program-counters which at any point in time, all contain the same value, with each individual processor either executing the common current instruction or remaining dormant for a step. In contrast, we allow each processor to be at a different point in the program. A MIMD machine has a different program for each processor. Our model is seen to be equivalent to a SIMD one, and to a reasonable subset of the MIMD model.

Finally, in the fourth section we justify our decision to start the computation with all processors active, rather than have them become active at run-time. This latter approach places a not altogether unreasonable upper-bound on the number of processors used in a computation, in relation to time. If we place a similar restriction on our model, then the two activation conventions are equivalent. However, we will see in Sections 6.1 and 6.2 that it is sometimes profitable to lift the restriction.

#### 3.1. The Basic Model

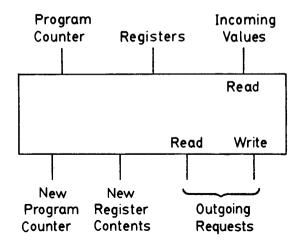

Our parallel machine model can be viewed as an infinite collection of interconnected, synchronous random-access machines, only finitely many of which are active in any particular finite computation. By "random-access machine" we refer to a variant of the RAM, which is already well-known as a sequential machine model (see, for example, [3,23,113]); and by "synchronous" we mean that the instruction-cycles of the RAMs are synchronized. Every RAM has an infinite number of general-purpose registers  $r_0, r_1, ...$ , each of which is capable of storing a single integer, and a read-only processor identity register PID. The PID of the i<sup>th</sup> RAM is preset to i, for i = 0,1,...

More formally, a *network* M consists of a program to be executed and a processor-bound which indicates how many processors are to be used. The *program* of M is a finite list of instructions; each instruction has the form either:

- (i) Read a value from a register of a neighbouring processor.

- (ii) Write a value to a register of a neighbouring processor.

- (iii) Perform an internal computation.

- (iv) Transfer of control.

For example, let "O" denote a binary operation defined on integers. For convenience we divide our example instruction-set into two categories. Local instructions have the form:

```

r_i \leftarrow \text{constant} (load register with constant)

r_i \leftarrow r_j \circ r_k (binary operation)

r_i \leftarrow r_r (indirect load)

r_r \leftarrow r_j (indirect store)

r_i \leftarrow PID (store PID)

halt (end execution)

goto m if r_i > 0 (conditional transfer of control)

```

Communication instructions have the form:

$$r_i \leftarrow (r_{r_j} \text{ of } r_k) \text{ (read)}$$

$(r_{r_i} \text{ of } r_i) \leftarrow r_k \text{ (write)}$

The program is to be executed synchronously in parallel by the (finitely many) active processors. As far as local instructions are concerned, their behaviour is that of independent RAMs, that is, references to registers in local instructions are treated as references to their respective local registers. Execution of a read instruction:

$$r_i \leftarrow (r_r, of r_k)$$

by processor p has the following effect. Suppose registers  $r_j$ ,  $r_k$  of processor p contain the values q and s respectively. Then the contents of register  $r_q$  of processor s are read and placed into register  $r_i$  of processor p. Similarly, execution of a write instruction:

$$(r_{r_i} \text{ of } r_j) \leftarrow r_k$$

by processor p has the following effect. Suppose registers  $r_i$ ,  $r_j$  of processor p contain the values q and s respectively. Then the contents of register  $r_k$  of processor p are written into register  $r_q$  of processor s.

Simultaneous reads (often called multiple reads or concurrent reads) of the same register are allowed. In the case of simultaneous writes to a single register we adopt some reasonable convention whereby a single processor succeeds and is allowed to write its value, whilst all others fail. For example (after [45]) the lowest-numbered processor attempting to write succeeds, or (as in Chapter 9), the processor which is attempting to write the smallest value succeeds, with ties being broken in favour of the lowest-numbered processor. A write-attempt always takes precedence over a local instruction, should any conflict occur. This is popularly called a CRCW (concurrent-read, concurrent-write) protocol. We will mostly be interested in CRCW networks, although occasionally (for example, in Section 6.3) we will consider CREW (concurrent-read, exclusive-write) networks, in which simultaneous writes are forbidden. EREW (exclusive-read, exclusive-write) models are also often studied in the literature (see, for example, Lev, Pippenger and Valiant [74] and Snir [118]). In the case of read-attempts conflicting with write-attempts, the reads are serviced first. Any attempt to write to a non-existent or halted processor is ignored. Any attempt to read from a non-existent or halted processor returns zero.

Suppose  $f: \mathbb{Z}^* \to \mathbb{Z}^*$  and  $x = \langle x_0, x_1, \ldots, x_{n-1} \rangle$ , where  $x_i \in \mathbb{Z}$  for  $0 \le i < n$ . We will say that x has size or length n, and write |x| = n. Let  $m = \max_{|x| = n} |f(x)|$  and  $f_n: \mathbb{Z}^n \to \mathbb{Z}^m$  denote the restriction of f to n arguments (we adopt the convention that unused output places are filled by zeros). We will variously refer to x as an input or input string, and each  $x_i$  as an argument or input symbol.

Suppose M is a network with processor-bound P:N $\rightarrow$ N. We assume that P is computable. Let p=P(n). A computation of M on input x is defined as follows. The input symbols are placed consecutively into register  $r_0$  of processors 0,1,.... If p < n we wrap around into register  $r_1$  of processors 0,1,... etc., utilizing in this fashion as many registers as necessary. That is, we place  $x_i$  into register  $r_{\lfloor i/p \rfloor}$  of processor (i mod p). All other general-purpose registers are set to zero. We then simultaneously activate processors 0,1,...,p-1. These synchronously execute the program of M. For  $0 \le i < m$  let  $y_i$  denote the contents of register  $r_{\lfloor i/p \rfloor}$  of processor (i mod p) when all processors have finally halted. We say that M computes f if for all  $n \ge 0$  and inputs x with |x| = n,  $f_n(x) = \langle y_0, y_1, \ldots, y_{m-1} \rangle$ . Recognition of a language over a finite alphabet is defined in the customary manner; we will encode each input symbol as a positive integer, and say that acceptance of an input occurs if register  $r_0$  of processor 0 contains the value 1 on termination of the computation.

Note that if  $P(n) \ge n$ , then the network can determine n, the input-size, in constant time, as follows. We simply adopt the convention that zero is never used as an input value, replacing every non-negative integer i in the input by i+1. Each processor j examines its register  $r_0$ . If it is non-zero, it then examines register  $r_0$  of processor j+1. If that is zero (and exactly one processor will find that this is the case), then the number of inputs is j+1, which value it writes to register  $r_1$  of processor 0. Each processor in possession of a positive input value then subtracts one from it, and finally all processors simultaneously read the number of inputs from register  $r_1$  of processor 0. For general P(n), this algorithm can be modified to run in time  $O(\frac{n}{P(n)} + 1)$ , which can be ignored for computations which depend on all n input symbols, since such a computation requires time  $O(\frac{n}{P(n)} + 1)$ .

The interconnection pattern of M is an infinite family of finite graphs  $G = (G_0, G_1,...)$ , one for each input-size. For  $n \ge 0$ ,  $G_n$  has vertex-set  $\{0,1,...,P(n)-1\}$ , and an edge between vertices i and j if at any time during the

computation of M on an input of length n, processor i attempts to read from or write to a register of processor j. Let  $D:N\to N$ . M is said to have degree D(n) if for all  $n \geq 0$ ,  $G_n$  has degree D(n).

Let  $T,S,W:N\to N$ . M is said to compute within time T(n) if for all inputs of size n, all active processors have halted within T(n) steps. For  $0 \le t \le T(n)$ , let  $S_t(n)$  be the maximum (over all inputs of size n) number of registers of M with non-zero contents after t instructions have been executed. Then M uses space S(n) if  $S(n) = \max_{0 \le t \le T(n)} S_t(n)$ . It has word-size W(n) if every value which appears in a register during such a computation has absolute value less than  $2^{W(n)}$  (note that this includes the inputs, outputs and processor identity registers).

The space bound is a measure of the number of registers used in a computation. It is slightly non-standard; it is more usual to define space to be the number of registers which are assigned non-zero contents at any point during the computation (see, for example, [3] for the case of a single RAM). Our reasons will become more apparent in Chapter 9. The word-size is a measure of the width of (inter- and intra-processor) data paths, and a measure of register size. This can be combined with our unit-cost measure of space to provide an upper-bound on log-cost space.

Consider the example instruction-set given earlier in this section. So far, we have not specified exactly which binary operations can be used for "o". In particular we will be interested in five types of instruction-sets.

1. The *minimal* instruction-set allows addition, subtraction and shifts of positive values by a single bit.

$$\begin{array}{c|c} r_i \leftarrow r_j \pm r_k \\ \\ r_i \leftarrow \left| r_j / 2 \right| \end{array}$$

Note that the second instruction corresponds to a right-shift by a single bit, and that a left-shift can be achieved by using integer addition.

2. The restricted arithmetic instruction-set also allows arbitrary-length shifts.

$$r_i \leftarrow \left\lfloor r_j * 2^{r_k} \right\rfloor$$

Note that  $r_k$  may be either positive (corresponding to a left-shift) or negative (corresponding to a right-shift). The "floor" operators are not necessary in the former case.

3. The full arithmetic instruction-set is the restricted arithmetic instruction-set augmented with multiplication and integer division.

$$\begin{aligned} &\mathbf{r}_i \!\!\leftarrow\!\! \mathbf{r}_j \!\!*\! \mathbf{r}_k \\ &\mathbf{r}_i \!\!\leftarrow\!\! \left \lfloor \mathbf{r}_j / \mathbf{r}_k \right \rfloor \end{aligned}$$

4. The extended arithmetic instruction-set is the full arithmetic instruction-set plus exponentiation.

$$r_i \leftarrow r_i^{r_k}$$

5. The general instruction-set includes any instruction which can be simulated by a multi-tape deterministic Turing machine in polynomial time. (That is, a multi-tape deterministic Turing machine can, when given as input the mbit binary representations of the operands, compute the binary representation of the result in time m<sup>O(1)</sup>.)

A number of questions spring to mind. Given that we have chosen a unit-cost measure of time (that is, we charge one unit of time for each instruction executed, regardless of the type of instruction or the size of its arguments), are these instruction-sets reasonable? Are they powerful enough? Too powerful? Natural? Clearly an unrestricted instruction-set which allows any computable function as a local instruction is too powerful, but what kind of instruction-set is reasonable? We will return to these questions in the next section.

Instead of writing algorithms in the low-level RAM language, we will follow the common practice of using a high-level language which can easily be translated into instructions of this form. We use the usual high-level constructs for flow-of-control, based on sequencing, selection and iteration. Variables of the form (x of processor i) will be taken as a reference to variable x of processor i. An unmodified variable x will be taken to mean (x of processor PID), that is, a local variable. For example, execution of the statement

by a network of P(n) processors causes the i<sup>th</sup> processor,  $0 \le i < P(n)$ , to compare its variable y with variable y of processor  $\lfloor i/2 \rfloor$ . If it finds that the former is less than the latter, then it executes statement<sub>1</sub>, otherwise it executes statement<sub>2</sub>. All processors execute this code in parallel. To aid synchronization, we assume that statement<sub>1</sub> and statement<sub>2</sub> are translated into blocks of code containing the same number of instructions, by filling with NO-OPs (such as  $r_0 \leftarrow r_0$ )

as necessary. All of the algorithms in this Monograph will maintain synchronization by virtue of this simple arrangement. As a notational convenience we may occasionally use concurrent and conditional assignments. Block-structuring will be indicated by indentation, in the customary fashion.

#### 3.2. The Unit-Cost Measure of Time

In Section 3.1 we defined the running-time of our parallel machines to be the number of instructions executed (synchronously) before all active processors have halted. That is, we charge a single unit of time for each instruction. This is termed a *unit-cost* measure of time. The use of unit-cost charging is potentially a contentious issue. The alternative is *log-cost* charging, whereby the cost of an instruction is expressed as a function of the size of its arguments, thus tying the time required for a particular computation to its word-size.

We follow Cook [22] in the belief that the major parallel resources of interest are time and hardware. We also believe that the important issues in the design of parallel algorithms are more clear-cut if these two resources are kept completely independent. A hardware measure should take into account the amount of memory used, which will depend upon the word-size. This makes the unit-cost measure of time more attractive, since it alone is independent of word-size, and thus hardware.

Even for purely sequential machines, the selection of unit-cost measures versus log-cost is of fundamental importance. Inter-simulations between various log-cost models (for example [3], Turing machines and log-cost RAMs) can be achieved with only a polynomial increase in time, whereas no such simulation can be obtained between unit-cost and log-cost models. For example, in time t a unit-cost RAM with multiplication can compute (without input) a value as large as  $2^{c+\Theta(1)}$ , whereas the same machine with log-cost charging can only compute a value as large as  $2^{t+\Theta(1)}$ .

From a purely practical standpoint, the choice of charging mechanism depends on the type of computation in question. If the word-size of an algorithm is sufficiently small compared to the word-size of the computer on which it is to be implemented, then the unit-cost measure is more applicable. Alternatively, if the values being manipulated grow very quickly with input-size, requiring the use of multi-word instructions for quite modest input lengths, then the log-cost measure is preferable.

This issue is neatly encapsulated in what Goldschlager and Lister [47] call the "sequential computation thesis". This states that time on all "reasonable" sequential models is polynomially related. This is motivated principally by the polynomial-time simulations of one log-cost model by another, but in fact breaks the models into two disjoint classes, those with unit-cost and those with log-cost measure of time. Members of the same class are polynomially related, but two models from different classes are not. Given this observation, the important question which must be addressed by any theoretical treatment is not "which model is better", but "which model is more accurate for the intended application". We believe that a unit-cost model is more suitable for the individual processors of a parallel machine.

The parallel analogue of the sequential computation thesis is the so-called "parallel computation thesis" [18,45]. This states that time on all "reasonable" parallel models is polynomially related. Furthermore, it attempts to characterize parallel computers by relating parallel time to a sequential resource. More precisely, it states that time on a "reasonable" parallel computer is polynomially equivalent to log-cost sequential (for example, Turing machine) space. This has two implications. Firstly, a machine which is too weak to simulate an S(n) space-bounded Turing machine in time S(n)O(1) is not powerful enough to be called a parallel machine. Secondly, a machine which is so strong that a T(n) time-bounded computation cannot be simulated in space T(n)O(1) by a Turing machine is too powerful to be called parallel. We will be concentrating mainly on the latter aspect of the parallel computation thesis, since networks with an unrestricted instruction-set are obviously extremely powerful. Henceforth, by "reasonable" we will mean "not too powerful", in the sense that it is "reasonable" to expect a parallel computer to have only a moderate amount of resources at its disposal.

As we shall see in Section 5.3, one way of making our model satisfy the parallel computation thesis is to restrict the processors to the minimal instruction-set of Section 3.1 (this approach was taken by Goldschlager for his SIMDAG [45]). This ensures that the word-size grows by at most one in every time-step, and so the log-cost of the individual instructions executed in any given computation is at most a polynomial in the unit-cost running-time, provided the input integers are sufficiently small. In this case, unit-cost and log-cost are polynomially related. It makes sense to restrict the word-size of parallel processors since (as we saw in the second paragraph of this section) the extra power of unit-

cost RAMs over log-cost RAMs seems to stem from their ability to generate large integers quickly. Indeed, a single unit-cost RAM with either the restricted [103] or full arithmetic [50] instruction-sets satisfies the parallel computation thesis, so is itself as powerful as a parallel machine.

We claim that the unit-cost measure of time is valid for parallel processors. We shall call this the unit-cost hypothesis. It is framed as a hypothesis (rather than a theorem or proposition) because it cannot be proved or disproved in the formal sense. In particular, it depends upon the way in which the word "valid" is interpreted. We will meet several interpretations in the remainder of this Monograph. Whilst it is intuitively obvious that the unit-cost measure of time is unrealistic for very powerful instruction-sets which allow the computation of infeasible functions in a single step, we may reasonably expect it to be realistic for fairly weak instruction-sets, such as the minimal instruction-set of Section 3.1.

This raises a number of interesting side-issues. We are in effect asking when a unit-cost model is "reasonable". We have seen that restricting the processors to the minimal instruction-set makes our model "reasonable" in the sense that it satisfies the parallel computation thesis. But what do we actually mean by "reasonable"? Do models which satisfy the parallel computation thesis successfully formalize the idea of "parallel computers"? What do we really expect from a parallel machine model? These are amongst the issues that we will address in Chapter 4.

#### 3.3. The Assignment of Programs to Processors

Although every processor of our parallel machine executes the same program, our model does not fall precisely into the SIMD category of Flynn [32]. SIMD is an acronym for "Single Instruction-stream, Multiple Data-stream" computer. In the latter, each processor has the same program, and shares the same program-counter. At each time-step, each processor either executes the common current instruction, or remains dormant for a step. This model is attractive since program-control can thus be left to a single central processor (as in Goldschlager [45]). This central processor broadcasts the current instruction to all processors, which individually decide whether to participate. In our model, the conditional goto instruction takes action depending on the value of a local register, the contents of which may vary from processor to processor. Thus different processors may be at different points in the program at any given time. However, it is fairly

easy to show that our model is equal in power to a SIMD one, and to a reasonable subset of MIMD models. MIMD is an acronym for "Multiple Instruction-stream, Multiple Data-stream" computer, and refers to a model in which each processor may have a different program.

For the sake of discussion, we will call our assignment of programs to processors a uniform one. We use the term "uniform" in the sense of Karp and Lipton [61], meaning that every machine has a finite description. In our case, the finite description consists of the program (a finite list of instructions) and the processor-bound (which can be represented as the Gödel number of a Turing machine which computes the binary representation of P(n), on input n in binary). A MIMD model is non-uniform in the sense that it allows a different program for each processor; thus an infinite family of finite descriptions (one for each input-size) is needed. Some authors (for example [15,22,108]) use the term "uniform" to denote the fact that an external "constructibility" condition has been enforced on a non-uniform model in order to restrict interest to machines with finite descriptions.

A SIMD machine is a uniform one in which, at any given point in time, all active processors are either executing the same instruction, or are dormant. Our high-level pseudo-programming language allows the user to write non-SIMD programs; we believe that this keeps the language simple, elegant and flexible (it may be argued that it gives the user the flexibility to get into trouble, but the same is often said of the *goto* statement in modern programming languages). Furthermore, it is not really necessary to force the programmer to write SIMD programs, since a uniform network can be simulated by a SIMD one without asymptotic time-loss, using the same number of processors and degree, with space and word-size increasing by only a constant.

Suppose M is a P(n)-processor uniform network. We will construct a SIMD network to simulate M as follows. Processor i of the SIMD network,  $0 \le i < P(n)$ , simulates processor i of M, using variables PC, VPC, NPC, PR, A and V, and an infinite array R. PC keeps track of the program-counter of the simulated processor, whilst for  $j \ge 0$ , R[j] contains the current contents of its register  $r_j$ . VPC (the virtual program-counter) will cycle from 1 to the program length (which is a constant, independent of n); when PC = VPC the PC<sup>th</sup> instruction of the program of M is simulated. NPC receives the new program-counter value, and if the instruction involves a data-transfer, A and PR receive the address and PID respectively of the register to be updated, and V its new

value. At the end of the cycle, the arrays R are updated to reflect the new register contents, using the information in PR, A and V, whilst PC is updated using the contents of NPC. The process is completed at the end of a cycle in which a halt instruction is simulated.

We present the algorithm in the high-level language of Section 3.1. A different interpretation is placed on the control constructs however, in order to make them strictly SIMD. The branches of a selection statement (such as if or case) are tried one at a time, with a processor executing a particular branch if its register contents satisfy the entry condition; all other processors remain dormant during that period. This is opposed to the general (non-SIMD) uniform case, in which all processors are free to start their respective branches at the same time, or to enter and leave the construct at different times.

Suppose M has the example instruction-set of Section 3.1. Then the program of the simulating network is as follows:

```

A := V := 0

PC:=VPC:=1

while PC > 0 do

for VPC:=1 to program length do

if VPC = PC then

PR.A.V:=case PCth instruction of M of

"r, -constant":PID, i, constant

r_i \leftarrow r_i \circ r_k:PID,i,R[j]\circR[k]